I2S/TDM Multichannel Audio Transceiver

The I2S-TDM IP core is a configurable, full-duplex, multichannel serial audio transceiver.

Overview

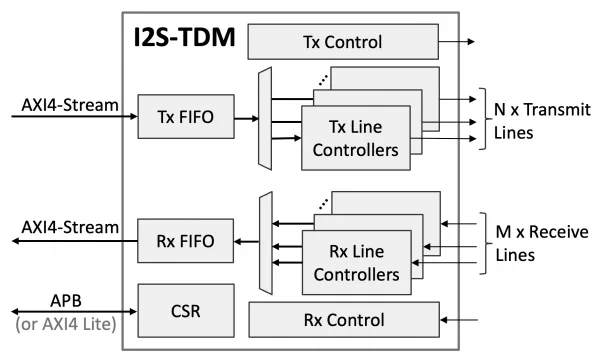

The I2S-TDM IP core is a highly configurable, full-duplex, multichannel serial audio transceiver. The transceiver can act as a controller (master) or a target (slave) for Inter-IC Sound (I2S) and Time-Division Multiplexed (TDM) audio interfaces, exchanging mul-ti-channel audio samples over a configurable number of serial lines (pins).

The I2S-TDM offers a number of configuration options to satisfy a wide range of serial audio interface requirements. The operation mode (controller or target), sample width, sample rate, frame format, number of channels and their allocation to physical lines are all programmable at run time. At synthesis time, designers can choose the maximum number of audio channels and serial data lines the transceiver can support.

The core is designed for ease of use and integration and adheres to the industry’s best coding and verification practices. The core’s control and status registers (CSR) are accessed through a 32-bit AMBA® APB interface, or, optionally, an AXI4 Lite inter-face. The host system exchanges audio data with the core either via this CSR interface or via dedicated AXI4-Stream interfaces. The system interfaces operate with a clock that is independent from the audio master and serial bit clocks, and the core implements clean clock domain crossing boundaries.

Key features

- Serial Audio Transceiver

- Supports left-justified and right-justified I2S and TDM audio data formats

- Full-duplex operation

- Configurable number of receive and transmit data lines (pins), and number of audio channels

- Software-Controlled Parameters per Direction (Tx and Rx)

- Controller (master) or target (slave) mode of operation

- Sample width of 2 to 32 bits,

- Sample rate (bit clock period and polarity)

- Frame format (Fsync/WS duration, delay and polarity)

- Implemented serial data lines and number of channels per line

- Synthesis Time Configuration Options

- Number of transmit and receive serial data lines

- Maximum number of transmit and receive audio channels

- Receive and Transmit FIFO size

- SoC System Interfaces

- 32-bit AMBA APB or AXI4 Lite for control and status register access

- Audio data input/output via register interface, or via dedicated 32-bit AXI-Stream interfaces

- Maskable interrupts based on programmable FIFO occupancy thresholds

Block Diagram

What’s Included?

- LINT-clean Verilog RTL source code or targeted FPGA netlist

- Integration Test-Bench

- Simulation & synthesis scripts

- Comprehensive user documentation

- FPGA evaluation boards available on request

- Bare-metal device drivers

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about I2S IP core

FPGAs - The Logical Solution to the Microcontroller Shortage

Paving the way for the next generation audio codec for True Wireless Stereo (TWS) applications - PART 2 : Increasing play time

Enabling AI Vision at the Edge

CSoC Platform / Digital Subsystem IP for IoT

Growing audio requirements in SoCs

Frequently asked questions about I2S IP cores

What is I2S/TDM Multichannel Audio Transceiver?

I2S/TDM Multichannel Audio Transceiver is a I2S IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this I2S?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2S IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.