I2S Verification IP

I2S Verification IP provides an smart way to verify the I2S bi-directional two-wire bus.

Overview

I2S Verification IP provides an smart way to verify the I2S bi-directional two-wire bus. The SmartDV's I2S Verification IP is fully compliant with version Philip's I2S-Bus Specification June 5, 1996 and provides the following features.

I2S Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

I2S Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Complies with Philips I2S Specification June 5, 1996

- Full I2S Transmitter, Receiver and Controller functionality

- Supports up to 32 channels in transmit path

- Supports up to 32 channels in receive path

- Supports programmable word length 8,12,16,20,24,32

- Supports programmable padding

- Supports programmable bit reversal

- Supports left and right justified

- Both transmitter and receiver can either work with SCK as input or can drive SCK

- Supports programmable data rate on transmit path

- Can operate as master or slave in several configurations

- Master or slave mode as transmitter

- Master or slave mode as receiver

- Master mode as controller (does not transmit or receive data)

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Status counters for various events on bus.

- Callbacks in transmitter, receiver and monitor for various events.

- Supports constraints Randomization.

- Built in functional coverage analysis.

- I2S Verification IP comes with complete test suite to test every feature of I2S specification.

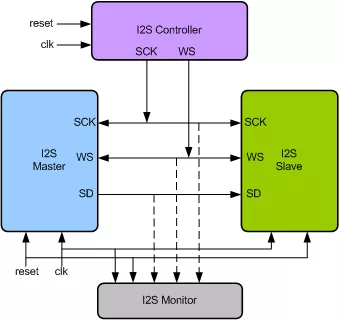

Block Diagram

Benefits

- Faster testbench development and more complete verification of I2S designs.

- Easy to use command interface simplifies testbench control and configuration of master and slave.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the I2S testcases.

- Examples showing how to connect various components, and usage of Master, Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about I2S IP core

FPGAs - The Logical Solution to the Microcontroller Shortage

Paving the way for the next generation audio codec for True Wireless Stereo (TWS) applications - PART 2 : Increasing play time

Enabling AI Vision at the Edge

CSoC Platform / Digital Subsystem IP for IoT

Growing audio requirements in SoCs

Frequently asked questions about I2S IP cores

What is I2S Verification IP?

I2S Verification IP is a I2S IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this I2S?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2S IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.