Ethernet PCS 100G

Silicon agnostic implementation of the Physical Coding Sublayer (PCS) compliant with Ethernet standard IEEE 802.3-2018 supporting…

Overview

Silicon agnostic implementation of the Physical Coding Sublayer (PCS) compliant with Ethernet standard IEEE 802.3-2018 supporting 100G line rates

The Ethernet PCS 100G IP core is a silicon agnostic implementation of the Physical Coding Sublayer (PCS) described in the Ethernet standard IEEE 802.3-2018 and compliant with Clause 82 of IEEE 802.3ba and Clause 91 of IEEE 802.3bj specification.

The Ethernet PCS 100G IP supports 100G line rates, however other Ethernet PCS speeds are available, such as 1G/2.5G and 10G/25G.

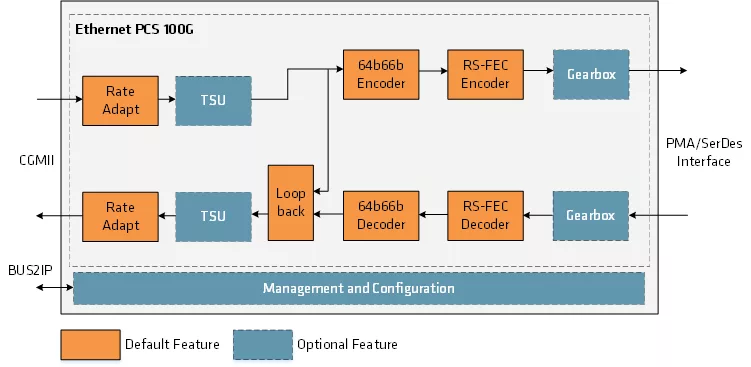

The Ethernet PCS 100G IP provides an interface between the Media Access Control (MAC) and Physical Medium Attachment (PMA) through a 4-lane parallel interface and offers a CGMII interface on the other side.

The Ethernet PCS 100G IP core is verified using advanced methodologies for RTL design, verification, HW verification and interoperability testing. It has been optimized for size and is a highly tested solution that will fast track any project.

Key features

Delivers Performance

- Supports Ethernet speed of 100G

- Complete 100GBASE-R with RS-FEC solution

- Can be used in common 100G Ethernet PHY applications

Feature Rich

- Configurable for several operating modes and speeds

- Works with multiple SerDes widths

- Clause 81 Reconciliation Sublayer (RS) and Media Independent Interface for 100 Gb/s operation (and CGMII)

- Clause 82 Physical Coding Sublayer (PCS) for 64B 66B, type 100GBASE-R

- Clause 91 Reed-Solomon Forward Error Correction (RS-FEC) sublayer for 100GBASE-R PHYs

- Clause 45 Management Data Input/Output (MDIO) Interface

- 64B 66B encoding/decoding

- Time Synchronization can optionally be included

Highly Configurable

- BUS2IP is the default Slave PHY Management interface, with AXI, APB, MDIO being optional

- Easy interfacing to standard MACs

- Several common control bus standards are supported

- Can be delivered with integrated MAC for plug and play

- Includes test pattern Generator/Checker

Silicon Agnostic

- Designed in SystemVerilog and targeting both ASICs and FPGAs

Block Diagram

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is Ethernet PCS 100G?

Ethernet PCS 100G is a Single-Protocol PHY IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.