UDP Offload Engine for IPv4

Atomic Rules UDP Offload Engine (UOE) is a UDP FPGA IP Core that allows for immediate operation at 10, 25, 40, 50, 100 or 400 GbE.

Overview

Atomic Rules UDP Offload Engine (UOE) is a UDP FPGA IP Core that allows for immediate operation at 10, 25, 40, 50, 100 or 400 GbE.

Interoperability with the Internet Protocol

The UDP/IP core implements the UDP/IPv4 standard RFC 768/791, including checksum, segmentation and reassembly hardware offload.

The UDP/IP core is tested for operation with popular FPGA vendors’ GbE Ethernet MACs.

Increase data transfer rates to 50/100/400 GbE without starting over

Allows for immediate operation at 10, 25 or 40 GbE, while providing a simple path to 50/100/400 GbE.

Offloads all UDP operations so you can work with datagrams

Offloads UDP standard RFC 768 from software to hardware.

L4 UDP Multicasts are pre-selected so that your application doesn’t have to perform this function

An integral IGMPv2 multicast pre-selector removes unwanted traffic.

Key features

- Concurrent datagram send and receive

- Ethernet packet: programmable frame MTU up to 16K Bytes (Super-Jumbo Frame support)

- UDP packet arbitrary datagram PDU up to IPv4 limit of 64K Bytes

- 16 Entry ARP cache (RFC 826)

- ICMP (unsegmented echo response message type only, used by “ping”)

- VLAN (IEEE 802.1Q) support

- Layer 3 direct, allowing non-UDP application connectivity

- Statistics accessible by control-plane interface

- Low-Area implementation, allowing multiple core instances per FPGA

- Avalon and AXI4 interfaces

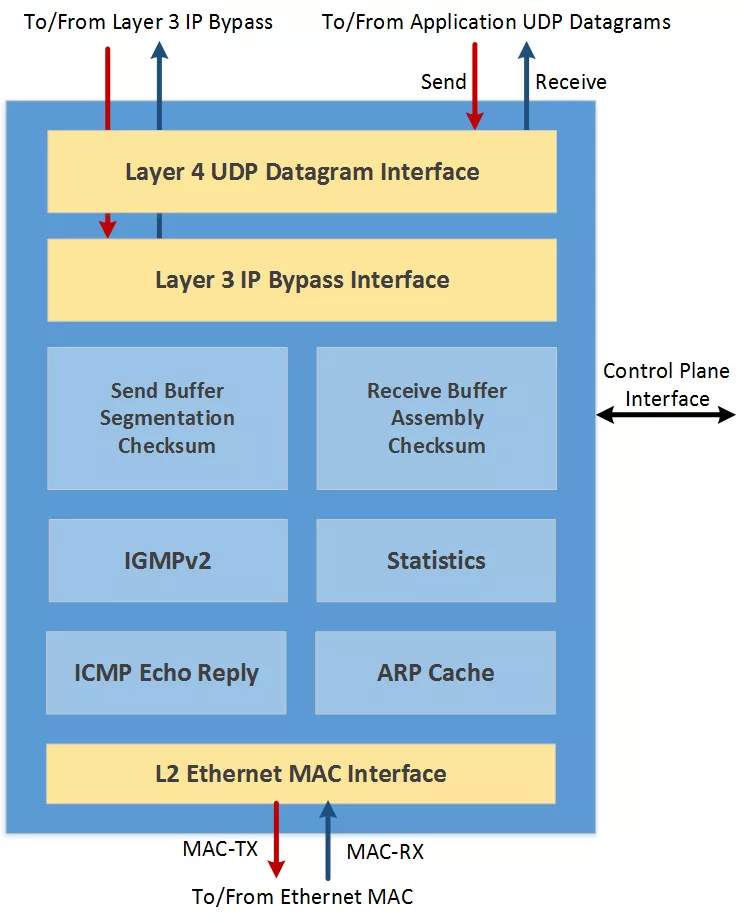

Block Diagram

Benefits

- Future proof your application; optimize throughput for all line rates

- Operates at 10, 25, 40, 50, 100, or 400 GbE

- Run full line rate with no packet loss, even for very small packets

- Offloads UDP standard RFC 768 from software to hardware

- Robust multicast support

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is UDP Offload Engine for IPv4?

UDP Offload Engine for IPv4 is a Ethernet IP core from Atomic Rules LLC listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.