LDO Voltage Regulator, 250 mA, TSMC N3P

LDO Voltage Regulator, 250 mA, Adjustable 0.45 V to 0.9 V Output The LDO IP is a 1.2V low-quiescent-current adjustable output vol…

Overview

LDO Voltage Regulator, 250 mA, Adjustable 0.45 V to 0.9 V Output

The LDO IP is a 1.2V low-quiescent-current adjustable output voltage Low-Drop-Out (LDO) Linear Regulator implemented in the TSMC 3nm N3P CMOS process technology. Its low sleep current, 250 mA maximum current, output voltage adjustability and precision make it especially suitable for use as an integrated voltage regulation source for subsystems implemented in analog, digital, mixed-signal and RF ASICs and SoCs

Key features

- TSMC 3nm FinFET process

- Input voltage: 1.2 V

- Output voltage range: 0.45 V to 0.9 V

- Vout adjustable in 50 mV increments

- Load current: 250 mA (max)

- PSRR:

- 36 dB @ < 1 KHz

- PSSR: 12 dB @ > 10 MHz

- < 50 mV undershoot/overshoot for load transients 1 A/ns

- Compact area

- Capless stable operation

- Functional from -40°C to 125°C

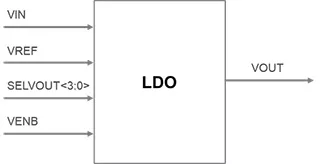

Block Diagram

What’s Included?

- SPICE netlist

- GDSII

- Behavioral Model

- IP Datasheet

- User’s Guide

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 3nm | N3P | Silicon Proven |

Specifications

Identity

Provider

Learn more about LDO Voltage Regulator IP core

Power Management for Internet of Things (IoT) System on a Chip (SoC) Development

Power management poses challenges

Tradeoffs of LDO Architectures and the Advantages of Advanced Architecture "Capless" LDOs

Key considerations and challenges when choosing LDOs

Introduction to Low Dropout (LDO) Linear Voltage Regulators

Frequently asked questions about LDO Voltage Regulator IP cores

What is LDO Voltage Regulator, 250 mA, TSMC N3P?

LDO Voltage Regulator, 250 mA, TSMC N3P is a LDO Voltage Regulator IP core from Silvaco, Inc. listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this LDO Voltage Regulator?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this LDO Voltage Regulator IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.