CPRI 6.1

Well established, field proven and silicon agnostic IP core conforming to CPRI 6.1 specifications Common Public Radio Interface (…

Overview

Well established, field proven and silicon agnostic IP core conforming to CPRI 6.1 specifications

Common Public Radio Interface (CPRI) 6.1 core is a silicon agnostic implementation of the CPRI 6.1 specification, which is targeting both ASIC and FPGAs. CPRI is a high-speed serial interface designed to meet or exceed the requirements of base band systems, C-RAN switches, Digital Front-End (DFE) processors or advanced test systems. With its extreme flexibility and reduced logic consumption, the CPRI 6.1 IP core is the perfect match whether the application is REC (Radio Equipment Controller) or RE (Radio Equipment).

The core can be dynamically configured to handle wireless multi-mode radio systems implementing deterministic latency features and high-performance throughputs required by LTE-A and 5G radio base stations.

The CPRI cores come in several versions to suit any implementation scenario whether speed, a compact size or a wide feature set is required. Chip Interfaces can offer a 64-bit version of the IP core which ensures easy time-closure even at the highest speeds.

CPRI 6.0 IP is developed to be silicon agnostic and can easily be tested in FPGA before integration into ASIC. The architecture has been optimized and hardware validated to deliver a robust solution.

Key features

- Delivering Performance

- CPRI Specification V6.1 features implemented

- Modular design with full feature set available

- Up to 64 antenna carriers per core

- Supports line-rates 1-9 (up to 12,16512 Gbps)

- Dynamic mapping configuration

- Richly Featured

- All mapping methods available (1, 2 and 3)

- Accurate delay measurements and calibration

- Size optimized Ethernet GMII interface

- RS-FEC

- Scrambling

- Rate Auto-Negotiation

- Daisy Chaining Interface

- Easy to use

- Testbench with typical system configuration and examples

- Easy integration

- Silicon Agnostic

- Designed in VHDL and targeting both ASICs and FPGAs

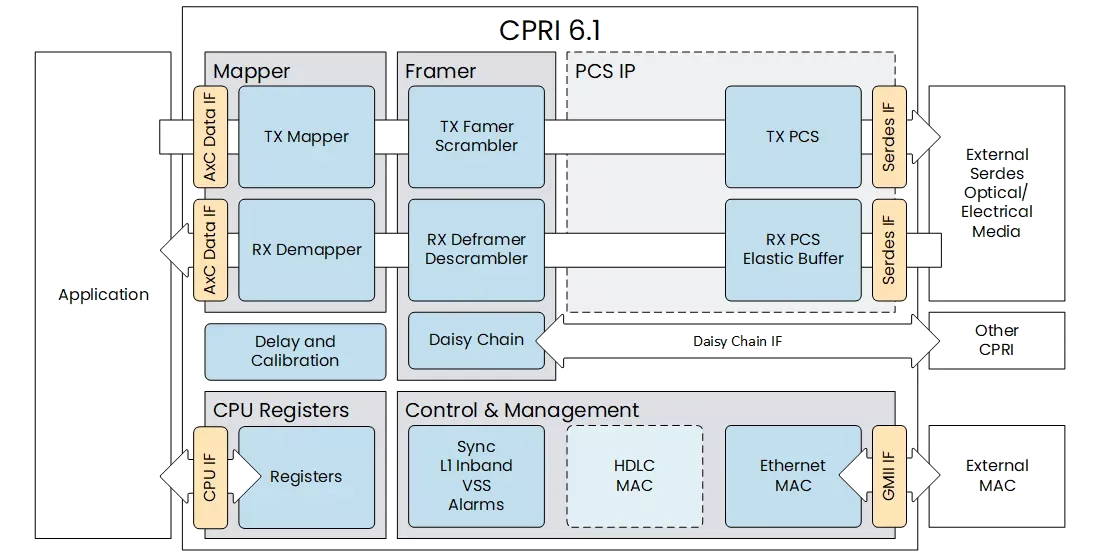

Block Diagram

Benefits

- Test Environment: CPRI 6.1 IP is tested against a VIP model in UVM regression for full functional coverage

- Silicon Agnostic: Optimized for ASIC but can be synthesized for most FPGAs

- Interoperability Tested: Multiple field deployments and tested against CPRI references

- Radio Expertise: IP with rich feature set designed by pioneers in radio solutions

- Active Support: All support is actively provided by engineers directly

What’s Included?

- The IP Core can be delivered in Source code or Encrypted format.

- The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Comcores Engineers.

- Synopsys Lint and CDC (optional)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPRI IP core

Low-loss compression of CPRI baseband data

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

O-RAN Fronthaul Security using MACsec

Seize the Ethernet TSN Opportunity

Part 2: Opening the 5G Radio Interface

Frequently asked questions about CPRI IP cores

What is CPRI 6.1?

CPRI 6.1 is a CPRI IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this CPRI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPRI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.