CPRI Verification IP

The SmartDV's CPRI Verification IP is fully compliant with CPRI Specification V4.2/V5.0/V6.0/V6.1 and V7.0 and verifies CPRI inte…

Overview

The SmartDV's CPRI Verification IP is fully compliant with CPRI Specification V4.2/V5.0/V6.0/V6.1 and V7.0 and verifies CPRI interfaces. It includes an extensive test suite covering most of the possible scenarios. It performs all possible protocol tests in a directed or a highly randomized fashion which adds the possibility to create the widest range of scenarios to verify the DUT effectively.

CPRI Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

CPRI Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Compliant with CPRI Specification V4.2/V5.0/V6.0/V6.1/V7.0

- Complete CPRI Tx/Rx functionality.

- Supports the Physical link layer (Layer 1) of the CPRI specification.

- Supports different standard line bit rates of the CPRI specification

- 614.4 MBPS

- 1228.8 MBPS

- 2457.6 MBPS

- 3072.0 MBPS

- 4915.2 MBPS

- 6144.0 MBPS

- 8110.08 MBPS

- 9830.4 MBPS

- 10137.6 MBPS

- 12165.12 MBPS

- 24330.24 MBPS

- Supports scrambler as in CPRI specification.

- Scrambler can be enabled or disabled.

- Supports insertion of scrambler errors.

- Supports disparity and invalid code insertion in 8B/10B.

- Supports 8B/10B line coding for bit rates upto 9830.4 MBPS

- Supports 64B/66B line coding without RS-FEC for 8110.08, 10137.6, 12165.12 and 24330.24 bit rates

- Supports 64B/66B line coding with RS-FEC for 24330.24 MBPS bit rate

- RS-FEC with alignment marker and without scrambler support

- RS-FEC without alignment marker and with scrambler support

- RS-FEC without alignment marker and without scrambler support

- Performs CPRI Hyperframe Framing

- Performs interleaving of IQ data, sync, C&M data, and vendor specific information

- Provides an 8-bit, 16-bit, or 32-bit for IQ data

- Performs subchannel mapping:

- Supports a slow C&M channel based on a serial HDLC interface at following standard HDLC bit rates

- 240 KBPS

- 480 KBPS

- 960 KBPS

- 1920 KBPS

- 2400 KBPS

- 3840 KBPS

- 4800 KBPS

- 7680 KBPS

- HDLC bit rate negotiated on higher layer

- Supports a fast C&M channel based on a serial Ethernet interface.

- Performs synchronization and timing

- Supports the L1 Inband Protocol

- Provides a parallel interface for merging vendor specific data into the CPRI frame

- Provides a start-up sequence state machine in hardware for both REC and RE nodes which performs:

- L1 Synchronization

- Protocol setup

- C&M Plane setup

- Supports Link Maintenance

- LOS detection

- LOF detection

- RAI indication

- SDI indication

- Detects and reports the following errors

- Invalid control character

- Invalid data character

- Scrambler errors

- Disparity errors

- Invalid 10bit code group errors

- Undersize and oversize frame errors

- CRC errors

- Framing errors

- LOS and LOF errors

- Block sync bits error

- Block encoding error

- RS-FEC alignment marker error

- RS-FEC parity error

- Glitch insertion and detection.

- Monitors, detects and notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- Supports constraints Randomization.

- Status counters for various events on bus.

- Supports bus accurate timing and timing checks.

- Callbacks in Master, Slave and Monitor for user processing of data.

- CPRI Verification IP comes with complete test suite to test every feature of CPRI specification.

- Functional coverage for complete CPRI features.

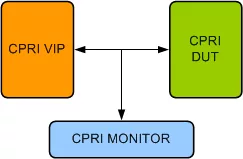

Block Diagram

Benefits

- Faster testbench development and more complete verification of CPRI designs.

- Easy to use command interface simplifies testbench control and configuration of Master and Slave.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the CPRI testcases.

- Examples showing how to connect various components, and usage of Master,Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPRI IP core

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

O-RAN Fronthaul Security using MACsec

Seize the Ethernet TSN Opportunity

Part 2: Opening the 5G Radio Interface

Accelerating 5G virtual RAN deployment

Frequently asked questions about CPRI IP cores

What is CPRI Verification IP?

CPRI Verification IP is a CPRI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this CPRI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPRI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.