Clock Attack Monitor

The agileCAM is a Ring Oscillator (RO) based clock attack monitor designed to detect clock attacks due to violation of the set-up…

Overview

The agileCAM is a Ring Oscillator (RO) based clock attack monitor designed to detect clock attacks due to violation of the set-up time requirements of critical circuits. agileCAM can detect attacks based on changes in clock frequency, clock hold and clock glitch errors. Additionally, it provides a relative frequency measurement of the monitored clock with programmable alarm thresholds. The RO based scheme is easily configurable depending on the frequency of the input clock and provides an area and power efficient solution. The agileCAM requires calibration and storage of the RO oscillation frequency at ATE testing of the device.

Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic, and repeatable, leading to analog IP that is more verifiable, more robust, and more reliable. Our methodology also allows us to quickly re-target our IP to different process options. We support all the major foundries including TSMC, GlobalFoundries, Intel Foundry, Samsung Foundry, UMC and Other Foundries.

Key features

- Input frequency: Up to 100 MHz

- Relative frequency measurement capability

- Relative frequency measurement resolution (frel): 10kHz

- Relative frequency measurement latency (trel): 100μs

- Detected clock attacks

- Over-clocking

- Under-clocking

- Glitching

- Holding/single-stepping

- Integrated calibration mode

- Silicon area – 0.02 mm2 in GF12LP+

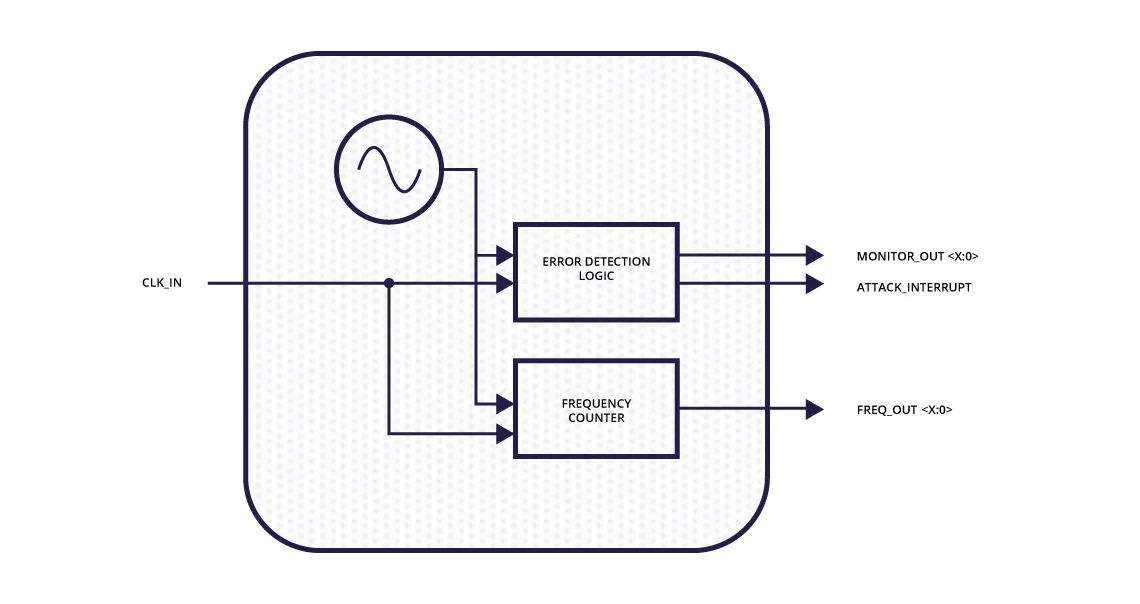

Block Diagram

Benefits

- Digitally-wrapped: AMBA-APB Interface to simplify integration, testing and operation

- Provided with System Verilog models DFT/DFM

- Provision for scan chain insertion

- Incorporated trim and calibration to facilitate process and/or manufacturing offsets to be adjusted

- Built-in test mode

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

What’s Included?

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Mixed Signal Subsystem IP core

Mixed Signal Design & Verification Methodology for Complex SoCs

Systematic approach to verification of a mixed signal IP - HSIC PHY case study

Customized PMICs with OTP in automotive and IoT

Effective Optimization of Power Management Architectures through Four standard "Interfaces for the Distribution of Power"

How to specify and integrate successfully a measurement analog front-end including its power computation engine in an energy metering IC

Frequently asked questions about Mixed-Signal Subsystem IP cores

What is Clock Attack Monitor?

Clock Attack Monitor is a Mixed Signal Subsystem IP core from Agile Analog listed on Semi IP Hub.

How should engineers evaluate this Mixed Signal Subsystem?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mixed Signal Subsystem IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.