IP Set for Miniaturized Telehealth Wearables

HealthIP™ is targeting portable health monitoring (telehealth/telemedicine) and wearable health monitoring devices.

Overview

HealthIP™ is targeting portable health monitoring (telehealth/telemedicine) and wearable health monitoring devices. The IP set contain analog front-ends’ hard macro and synthesizable HDL with optional multicore 32-bit RISC MCU. The whole IP is silicon proven in CMOS 130 nm. Engineering samples available in QFN80 package with development board.

Key features

- electrocardiography (ECG)

- electromyography (EMG)

- skin temperature and resistance

- respiration rate

- oxygen saturation (SpO2)

- analyze health parameters (32-bit RISC MCU)

- digital interfaces: UART, SPI, I2C, CAN, Ethernet

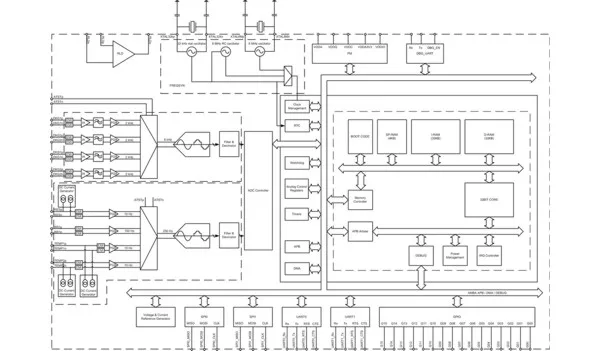

Block Diagram

Applications

- Analyze health parameters during sport

- Monitor people working in harsh and demanding conditions or in remote and inaccessible locations, such as: pilots, drivers, firefighters, miners, heavy machinery operators

- Elderly people portable monitoring

- Children and newborns portable monitoring

What’s Included?

- Datasheet/Integration Guide

- GDSII database/LVS & SPICE netlist

- HDL Model/Footprint (.LEF)

- IP implementation support, 6 months maintenance (delivery of the IP and documentation up-dates)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Mixed Signal Subsystem IP core

Mixed Signal Design & Verification Methodology for Complex SoCs

Systematic approach to verification of a mixed signal IP - HSIC PHY case study

Customized PMICs with OTP in automotive and IoT

Effective Optimization of Power Management Architectures through Four standard "Interfaces for the Distribution of Power"

How to specify and integrate successfully a measurement analog front-end including its power computation engine in an energy metering IC

Frequently asked questions about Mixed-Signal Subsystem IP cores

What is IP Set for Miniaturized Telehealth Wearables?

IP Set for Miniaturized Telehealth Wearables is a Mixed Signal Subsystem IP core from ChipCraft listed on Semi IP Hub.

How should engineers evaluate this Mixed Signal Subsystem?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mixed Signal Subsystem IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.