Sensor & Control IP Subsystem

Sensors are becoming increasingly ubiquitous.

Overview

Sensors are becoming increasingly ubiquitous. Many applications, such as those in the Internet of Things (IoT), automotive, and mobile markets increasingly rely on the ability to interpret a combination of environmental conditions such as pressure, temperature, motion, and proximity. By pre-integrating sensor and actuator-specific IP blocks together with software in a single subsystem, the vendor gives designers a complete, SoC-ready sensor and control solution that can significantly reduce their design and integration effort, lower design risk and accelerate time-to-market.

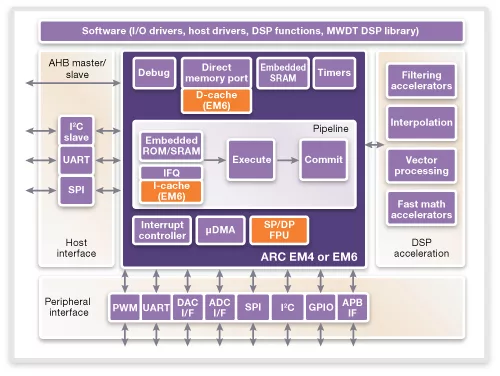

The ARC® Sensor and Control IP Subsystem is optimized to process data from digital and analog sensors, offloading the host processor and enabling more power efficient processing of sensor data. Faster application-specific control loops are driven via precision peripherals, and DSP single-cycle math computations and fractional arithmetic support. The fully configurable subsystem includes the choice of an ARC EM4 or EM6 processor, optional IEEE 754-2008 compliant FPU, integrated control peripherals, data converter interfaces, hardware accelerators, an extensive library of software DSP functions and I/O software drivers. The ARC Sensor and Control IP Subsystem provides designers with a complete, pre-verified solution that optimizes sensor fusion and actuator/motor control functions increasingly prevalent in automotive, mobile, industrial and IoT markets.

Key features

- Integrated, pre-verified hardware and software IP subsystem consisting of a choice of an ARC EM4 or EM6 processor, serial digital interfaces, data converter interfaces, hardware accelerators, software library of DSP functions and I/O drivers

- Optional IEEE 754-2008 compliant FPU reduces energy consumption by 10X for sensor applications executing floating point operations

- Integrated hardware accelerators for sensor-specific functions boost performance efficiency and reduce power consumption by up to 85% compared to discrete solutions

- Highly configurable with tightly integrated peripherals and dedicated hardware maximize sensor processing efficiency

- Extensive library of off-the-shelf software DSP functions, including mathematical, filtering, matrix/vector and decimation/interpolation, speeds application software development

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Mixed Signal Subsystem IP core

Mixed Signal Design & Verification Methodology for Complex SoCs

Systematic approach to verification of a mixed signal IP - HSIC PHY case study

Customized PMICs with OTP in automotive and IoT

Effective Optimization of Power Management Architectures through Four standard "Interfaces for the Distribution of Power"

How to specify and integrate successfully a measurement analog front-end including its power computation engine in an energy metering IC

Frequently asked questions about Mixed-Signal Subsystem IP cores

What is Sensor & Control IP Subsystem?

Sensor & Control IP Subsystem is a Mixed Signal Subsystem IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Mixed Signal Subsystem?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Mixed Signal Subsystem IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.