10-bit SAR ADC - XFAB XT018

The TS_ADC_10b_X8 is a 10-bit capacitive successive approximation register (SAR) Analog-to-Digital converter (ADC).

Overview

The TS_ADC_10b_X8 is a 10-bit capacitive successive approximation register (SAR) Analog-to-Digital converter (ADC). It operates with a 3.3 V analog power supply, a 1.8 V digital power supply, and an external voltage reference.

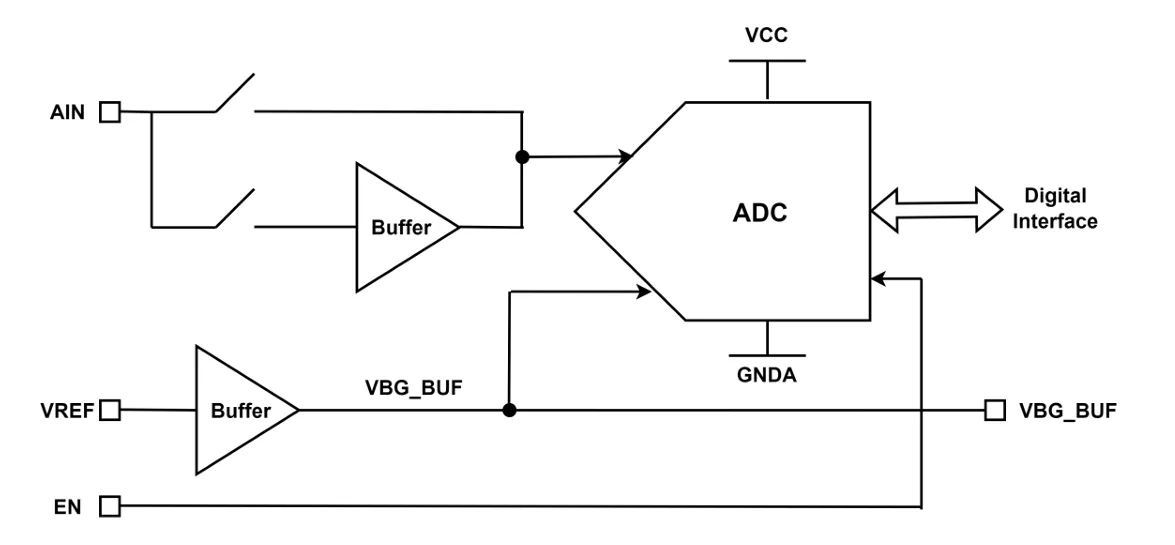

The ADC converts single-ended input voltages and requires no external S/H circuit. In addition to the ADC core, a buffer amplifier prevents the loading of the bandgap voltage reference generator by the ADC. The ADC can quantize inputs with either low or high source impedances. For inputs with high source impedances, an optional buffer amplifier can be configured.

A simple trimming mechanism is provided to compensate for deviations in the reference voltage. The sampling rate of the ADC is 125 kS/s. It achieves an integral nonlinearity (INL) between [-1.1 , +0.7] LSB and a differential nonlinearity (DNL) between [-0.9 , +0.8] LSB.

OPERATING CONDITIONS

| Parameters | Values |

| Junction temperature range | -40°C to +150°C |

| Supply voltage | 3.2 V to 3.4 V |

| Master clock frequency | 8 MHz |

| Input source impedance (for use without buffer amplifier) | 16 kΩ max |

| Reference voltage | 1.25 V typ. |

| ADC sampling time | 2.875 µs |

SPECIFICATION

| Parameters | Values |

| Operation DC current consumption on VCC | 900 µA max |

| Sampling capacitance | 18 pF typ. |

| Nominal resolution | 10 bit |

| Integral nonlinearity (INL) | -1.1 LSB to +0.7 LSB |

| Differential nonlinearity (DNL) | -0.9 LSB to +0.8 LSB |

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about ADC IP core

Time Interleaving of Analog to Digital Converters: Calibration Techniques, Limitations & what to look in Time Interleaved ADC IP prior to licensing

Three ways of looking at a sigma-delta ADC device

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Save power in IoT SoCs by leveraging ADC characteristics

High Speed ADC Data Transfer

Frequently asked questions about ADC IP cores

What is 10-bit SAR ADC - XFAB XT018?

10-bit SAR ADC - XFAB XT018 is a ADC IP core from TES Electronic Solutions listed on Semi IP Hub.

How should engineers evaluate this ADC?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this ADC IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.