Rapidus unveils new AI design tools for advanced semiconductor manufacturing

Tools will be released starting in 2026

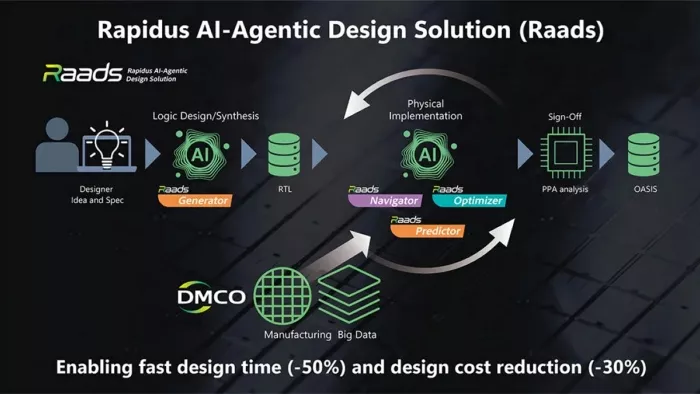

TOKYO, SEMICON Japan, Booth E5345, Dec. 17, 2025 – Rapidus Corporation today announced a new suite of AI design tools to support its Rapidus AI-Assisted Design Solution (Raads), a key initiative to helping to realize its Rapid and Unified Manufacturing Service (RUMS) concept. The technology approach will also be rebranded to Rapidus AI-Agentic Design Solution with multiple tools being released starting in 2026 and will be provided to customers together with a process design kit and reference flows. The new tools include:

- Raads Generator: An EDA tool based on large-scale language models (LLMs). When designers input semiconductor specifications, Raads Generator outputs register-transfer level (RTL) design data optimized for Rapidus’ 2nm manufacturing process.

- Raads Predictor: A tool for RTL debugging and optimization for physical design, placement and routing. Raads Predictor will provide a power performance area (PPA) estimate in a short period of time.

Designers can use Raads Generator to write design ideas and desired specifications as RTL source code and then input data into Raads Predictor along with Synopsys Design Constraints (SDC), allowing them to predict the PPA of the silicon manufactured by Rapidus.

Raads not only assists semiconductor designers with AI but will also become an AI agent for cutting-edge semiconductor device design. By utilizing Raads in conjunction with existing EDA tools, developers can reduce design time by 50% and design costs by 30%.

Following the launch of Raads Generator and Raads Predictor, Rapidus will also release additional tools throughout 2026 including:

- Raads Navigator / Raads Indicator: Utilizes LLMs to provide quality assurance and assistance to designers to derive solutions to design issues and problems.

- Raads Manager: A layout design tool that utilizes ML/AI to create a hierarchical configuration that minimizes design time.

- Raads Optimizer: Applies ML/AI to search for and derive parameters to optimize PPA.

Rapidus’ Innovative Integration for Manufacturing (IIM-1) foundry is introducing a single-wafer processing for all manufacturing processes. In June 2025, Rapidus connected more than 200 of the world’s most advanced pieces of semiconductor equipment to enable a completely new automated material handling system to support 2nm GAA prototyping. In July, Rapidus announced that prototyping had started at IIM-1 and the prototype wafers started to obtain their electrical characteristics.

About Rapidus Corporation

Rapidus Corporation aims to develop and manufacture the world’s most advanced logic semiconductors. We will create new industries together with our customers through the development and provision of services to shorten cycle times in design, wafer processes, 3D packaging, and more. We will continue to challenge ourselves in order to contribute to the fulfillment, prosperity, and happiness of people’s lives through the use of semiconductors.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related News

- Rapidus announces collaboration with Siemens for 2nm semiconductor design

- Cadence Design Systems Agrees to Plead Guilty and Pay Over $140 Million for Unlawfully Exporting Semiconductor Design Tools to a Restricted PRC Military University

- SEMIFIVE Secures AI Semiconductor Design Projects in Japan, Accelerating Global Expansion with New Local Subsidiary

- Denying China IC Manufacturing Tools

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard