OPENEDGES to Premiere PHY Vision 2.0 at Design Automation Conference 2024

Seoul, South Korea, June 19th, 2024 --- OPENEDGES Technology, Inc. (OPENEDGES), the leading provider of memory subsystem intellectual property (IP), is thrilled to unveil the live demo of the 2.0 release of PHY Vision, an advanced LPDDR PHY visualization and exploration software, at the Design Automation Conference (DAC) 2024. This event will take place at the Moscone Center West, from June 24th to 26th.

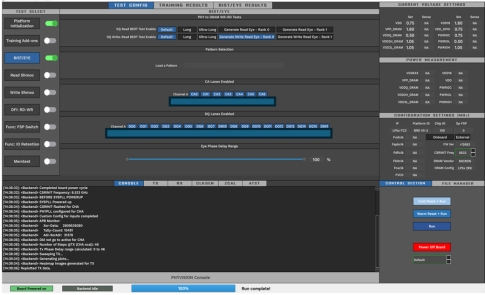

PHY Vision 2.0 is an intuitive Graphical User Interface (GUI) software that configures, controls and visualizes the behavior of OPENEDGES’ LPDDR PHY IPs, allowing customers to explore the impact of various PHY capabilities under different operating conditions and data rates.

The PHY Vision GUI was initially introduced at last year’s DAC and returns this year with significant enhancements, including architecture, performance, and portability improvements. The PHY Vision demonstration will feature OPENEDGES’ 7nm LPDDR5X combination PHY IP and test platform operating at 8533Mbps, the maximum data rate for LPDDR5X.

Image: A Screenshot from the PHY Vision 2.0 Software

In addition to seeing PHY Vision 2.0 in action, visitors to booth 2432 at the Moscone Center West can speak to OPENEDGES’ engineers to learn more about the unique benefits of their LPDDR PHY IP, including:

- Latest memory standards support for mature technology nodes

- Cross-verification with OPENEDGES’ ORBIT Memory Controller (OMC)

- Reduced silicon footprint and area requirements

- Accelerated training time with support for firmware customization

- Fast frequency set point (FSP) switching

- Optimized low power states

- Simplified integration of HARD and SOFT IP

“We are excited to showcase our newest PHY Vision 2.0 at DAC,” said Sean Lee, CEO of OPENEDGES Technology. “Since the company was founded in 2017, OPENEDGES has provided a comprehensive memory subsystem IP portfolio. This latest offering reflects our dedication to delivering sophisticated technologies that enable our customers to seamlessly and effectively integrate our DDR PHYs into their SoCs.”

Event Details:

Date: June 24th to 26th

Booth: #2432

Location: Moscone Center, San Francisco

To arrange a meeting with OPENEDGES at the event, please contact us at sales@openedges.com

For more information about the Design Automation Conference (DAC), visit www.dac.com

About OPENEDGES Technology, Inc.

OPENEDGES Technology, Inc. is a premier provider of memory subsystem IPs for the semiconductor industry. They offer a wide range of state-of-the-art solutions, including DDR memory controllers, DDR PHY, NoC interconnect, and NPU IPs that are widely adopted by customers worldwide. Their IPs comply with JEDEC standards, including LPDDR5x/5/4x/4/3, DDR5/4/3, GDDR6, and HBM3, ensuring their compatibility with the latest DDR technology trends. In 2019, they acquired The Six Semiconductor, Inc. (TSS), specializing in high-speed memory PHYs across multiple technologies. As a publicly listed company on the Korean Stock Exchange Market (394280. KQ), OPENEDGES is well-positioned to continue its growth and maintain its leadership in the memory subsystem IPs market.

Learn more about the company and its offerings by visiting the official website at www.openedges.com.

About The Six Semiconductor Inc. (TSS)

TSS is a Canadian technology company and a wholly owned subsidiary of OPENEDGES, specializes in developing advanced high-speed DDR PHY IP solutions that cater to a wide range of applications such as AI/ML, high-performance computing (HPC), mobile devices, and automotive. The company's product portfolio includes PHY IPs for various memory standards including LPDDR5x/5/4x/4, GDDR6, and HBM3, that are optimized for power and area. TSS's solutions are designed to be compatible with multiple technologies, foundries, and process nodes. The company's team of experts have a wealth of experience in the field, and are dedicated to providing the industry with high-quality and reliable DDR PHY IP solutions.

To learn more about TSS's products, visit their website at www.thesixsemi.com.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related News

- OPENEDGES Showcases Live Demo of PHY Vision at Design Automation Conference (DAC) 2023

- OPENEDGES Announces LPDDR5X/5/4x/4 PHY Tapeout at 7nm process node

- OPENEDGES Achieves Tapeout of LPDDR5x/5/4x/4 PHY IP on 5nm SF5A Process Technology

- OPENEDGES Proud to Announce the World's Only 7nm LPDDR5X PHY IP Operating at 8533 Mbps

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard