Instruction Smart Trace - really smart & non-intrusive?

Bytom, Poland -- November 6, 2014 -- Digital Core Design, celebrating its 15th anniversary on the IP Core market, enhanced its 8051 portfolio with the functionality of an Instruction Smart Trace. So, starting from the most popular DP8051, through the DP80390, to the world’s fastest DQ8051 – all of them, thanks to an IST, can efficiently reduce trace memory size and increase traced program history.

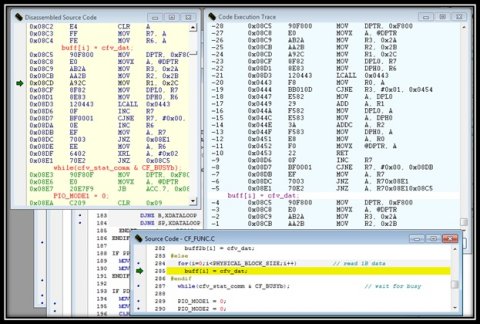

Instruction Smart Trace is an inherent part of the DoCDTM Hardware Debugger, which provides debugging capability of System-on-Chip (SoC). Unlike other on-chip debuggers, the tool provides non-intrusive debugging of a running application and saves designer’s time, thanks to the hardware trace, called Instructions Smart Trace buffer (IST). The DoCD-IST captures instructions in a smart and non-intrusive way, so it doesn’t capture addresses of all executed instructions, but only these related to the start of tracing, conditional jumps and interrupts. This method does not only save time, but also allows improving the size of the IST buffer and extend the trace history. - For example, by using 256 Bytes of trace memory, we can store 128 program branches and decode much more program history, since the executed program is composed of normal opcodes (mov, add, mul, anl, etc.) and branches – explains Tomek Krzyżak, VCEO of Digital Core Design. - Based on this information stored in IST hardware memory, our DoCD.exe and Keil driver decode executed program and display this information as an ASM code and C code in trace history – he adds.

Instruction Smart Trace is an inherent part of the DoCDTM Hardware Debugger, which provides debugging capability of System-on-Chip (SoC). Unlike other on-chip debuggers, the tool provides non-intrusive debugging of a running application and saves designer’s time, thanks to the hardware trace, called Instructions Smart Trace buffer (IST). The DoCD-IST captures instructions in a smart and non-intrusive way, so it doesn’t capture addresses of all executed instructions, but only these related to the start of tracing, conditional jumps and interrupts. This method does not only save time, but also allows improving the size of the IST buffer and extend the trace history. - For example, by using 256 Bytes of trace memory, we can store 128 program branches and decode much more program history, since the executed program is composed of normal opcodes (mov, add, mul, anl, etc.) and branches – explains Tomek Krzyżak, VCEO of Digital Core Design. - Based on this information stored in IST hardware memory, our DoCD.exe and Keil driver decode executed program and display this information as an ASM code and C code in trace history – he adds.

The DoCD Instruction Smart Trace buffer is configurable up to 8192 levels and is completely transparent for the debugged application. Its functionality enables real-time capture of executed instructions. Thanks to it, the engineer can later read-back to track-down the history of executed code, by using the DoCD debug software. – Instruction Smart Trace captures instructions in a smart and non-intrusive way, which means, that it doesn’t capture addresses of all executed instructions, but only instructions related to the start of the tracing, conditional jumps and interrupts – adds Krzyzak.

As an example, the trace buffer is 2kB, which means that up to 1024 levels can be captured. So there’s no wonder then, that it gives much greater history than 1024 instructions executed by the CPU. In the typical application IST enables to execute over 10k instructions, depending on how many conditional jumps and interrupts have been executed by the CPU.

As an example, the trace buffer is 2kB, which means that up to 1024 levels can be captured. So there’s no wonder then, that it gives much greater history than 1024 instructions executed by the CPU. In the typical application IST enables to execute over 10k instructions, depending on how many conditional jumps and interrupts have been executed by the CPU.

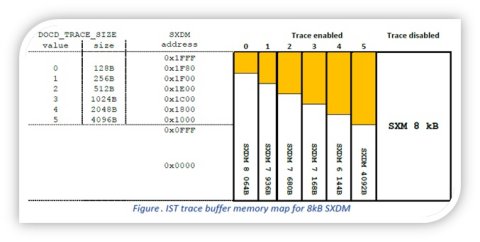

Instruction Smart Trace has also configurable start/stop triggers, so the engineer can easily set the condition at which instruction tracing starts, but also when it should stop. But this is still not all, because the trace buffer can be changed or disabled dynamically. The IST uses the end of SXDM memory space, that’s why it can share the trace memory with the debugged programs. And when the debugging is finished, it assigns the whole memory back to the application.

More information: http://dcd.pl/page/154/docd/

Information about Digital Core Design:

In 2014 Digital Core Design celebrates its 15th Anniversary. The company founded in 1999, since the beginning stands in the forefront of the IP Core market. High specialization and profound customer service enabled to introduce more than 70 different architectures. Among them is the world’s fastest 8051 IP Core, the DQ80251, which is more than 66 times faster than the standard solution. As an effect, over 300 hundred licensees have been sold to more than 500 companies worldwide. Among them are the biggest enterprises like e.g. Sony, Siemens, General Electric and Toyota. But a lot of DCD’s customers are small businesses, R&D laboratories or front/back end offices, which require exact solution tailored to their project needs. Rough estimations say that more than 250 000 000 devices around the globe have been based on Digital Core Design’s IP Cores.

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- MIPI CSI-2 CSE2 Security Module

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

Related News

- EDGEAI to Revolutionize Smart Metering with BrainChip Akida 2 License

- Mnano selects Dolphin Integration's six-channel Audio converter for its next generation of Smart Speakers

- HiTrend selects Dolphin Integration's cache controller for its next generation of smart energy metering chips

- Arm Drives Smart Utilities for KEPCO's Behind the Meter Project

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard