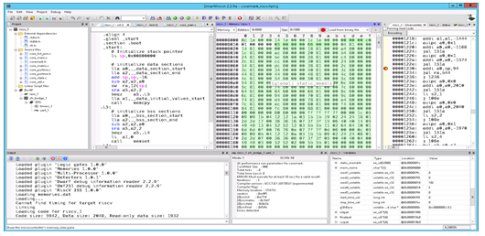

Dolphin Integration makes available in free download its innovative IDE SmartVision, for the RISC-V ecosystem

Meylan, France, June 4, 2018 -- Dolphin Integration announces the availability in free download of its innovative IDE SmartVisionTM supporting the RISC-V Instruction Set Architecture (ISA).

A suitable software development environment is fundamental for optimizing designs in terms of power consumption, area (code density) and performances. Thanks to its IDE, Dolphin integration enables early in the design flow to meet these requirements.

SmartVisionTM is an open environment allowing the design of complete subsystems based on processor cores and peripherals. It provides an intuitive interface as well as the necessary tools to debug embedded software by simulation or by In Circuit Emulation. Its key benefits include:

- an API to describe behavioral models of new components

- advanced debug features with a breakpoint composer for complex behavior analysis

- a versatile solution for embedded software debug by using In Circuit Emulation with FPGA/ASIC and by simulating a Cycle Accurate Bit Accurate (CABA) model

- a power optimization and estimation solution

- the Built-In-Real-time Debugger, BIRD, a debug unit, with JTAG interface

The support of RISC-V through the RV32 Tornado subsystem offers a complete turnkey solution to configure and optimize ultra-low power SoCs. It includes:

- RISC-V Instruction Set Simulator with configurable timing annotations

- RISC-V toolchain (GCC)

- RISC-V musl libraries precompiled for diverse RISC-V extensions

Furthermore, for easy compatibility with the RISC-V ecosystem, the support of the upcoming debug specification is in progress.

The SmartVisionTM IDE is in free download. For more information, please contact us at contact@dolphin.fr

About Dolphin Integration

Dolphin Integration is a pioneer in Energy-Efficient Systems-on-Chip enablement. The company serves a growing range of applications from battery-operated to line-powered. Its portfolio of more than 200 silicon IPs covering Foundation, Feature and power Fabric IPs are proven and available in multiple processes and foundries. This coherent portfolio allows to reduce SoC power consumption in sleep, triggering and active processing modes. The company is committed to its customer success through constant innovation, quality control and dedicated support. Dolphin Integration comes with 30 years experience in integration of silicon IP components leveraging power-integrity driven simulation tools to design and supply cost-effective logic and mixed-signal ASIC/SoC.

Related Semiconductor IP

- RISC-V IOPMP IP

- RISC-V Debug & Trace IP

- Gen#2 of 64-bit RISC-V core with out-of-order pipeline based complex

- 64-bit RISC-V core with in-order single issue pipeline. Tiny Linux-capable processor for IoT applications.

- Tiny, Ultra-Low-Power Embedded RISC-V Processor

Related News

- Dolphin Integration announces a new release of its innovative IDE for the RISC-V ecosystem

- Feature-rich RISC-V IDE Available for Free Download

- Nero Introduces Reference Quality Nero Digital Audio MPEG-4 and 3G Encoding Software; Free download is available for personal use via Nero website

- ZiLOG(R) to Offer Developer Studio II Software via Free Download

Latest News

- Wind River Joins the CHERI Alliance and Collaborates with Innovate UK to Accelerate Cybersecurity Innovation

- Arteris and MIPS Partner to Accelerate Development for Physical AI Platforms

- DCD-SEMI expands CryptOne with EdDSA Curve25519 IP core for secure embedded systems

- Syntacore's SCR RISC-V IP Now Supports Zephyr 4.3

- Xylon Presents New 12-Channel GMSL3/GMSL2 FMC+ ExpansionBoard