新思科技DesignWare 112G Ethernet PHY IP经验证可用于5nm制程高性能计算SOC,具有更佳PPA

DesignWare IPå ·ææ ä¸ä¼¦æ¯çé¿è·ç¦»è¿æ¥æ§è½ï¼æ¯æ大äº40dBçæå ¥æèï¼å¹¶æä¾ä½äº5 pJ/Bitçåèæç

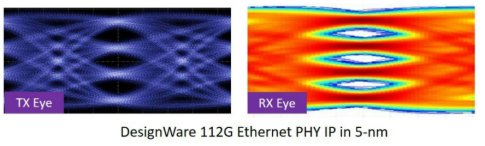

å å©ç¦å°¼äºå·å±±æ¯å2021å¹´2æ22æ¥ -- æ°æç§æ ï¼Synopsys, Inc., 纳æ¯è¾¾å è¡ç¥¨ä»£ç ï¼ SNPSï¼è¿æ¥å®£å¸ï¼ DesignWare®112G EthernetPHY IPå·²è·å¾å¨5nm FinFETå·¥èºä¸çç¡ è®¤è¯ï¼å ·ææ¾èçæ§è½ãåçåé¢ç§¯ä¼å¿ãå¾çäºDesignWare 112G以太ç½PHYçé¢ç§¯æçï¼å¼åè è½å¤ä½¿ç¨å¯æç¥å¸å±çIPæ ¸æ¥ä¼åé«å¯åº¦ççä¸ç³»ç»ï¼SoCï¼ï¼éè¿æ大é度å°å¨è£¸ççåè§è¿è¡å å åå¸å±æ¥æé«è¾¹å¸¦å®½ã为äºæé«æ§è½ï¼DesignWare 112G PHYå¨å¤§äº40dBçééä¸å±ç¤ºäºååçº éåçé¶è¯¯ç çï¼åæ¶å ·æä½äº5 pJ/bitçèè½ææã

â

â

æ°æç§æå ¨é¢ç112G以太ç½PHY解å³æ¹æ¡ç»åäºèªèº«çå¸çº¿å¯è¡æ§ç 究ãå°è£ åºæ¿æåãä¿¡å·åçµæºå®æ´æ§æ¨¡å以åæ·±å ¥ç串æ°åæï¼å¯å®ç°å¿«éå¯é çSoCéæãDesignWare 112G以太ç½PHYæ¯æ°æç§æé¢åé«æ§è½äºè®¡ç®åºç¨ç综åIP产åç»åçä¸é¨åï¼é¤æ¤ä¹å¤è¿å æ¬å¹¿æ³ä½¿ç¨çåè®®å¦PCI Express ®ãDDRãHBMãDie-to-DieãCXLå CCIXã

æ°æç§æIPå¸åºè¥éåæç¥é«çº§å¯æ»è£John Koeter表示320å¤å¹´æ¥ï¼æ°æç§æä¸ç´æ¯ä¸çå¯ä¿¡èµçIPä¾åºåï¼è´åäºä¸ºå¼åè æä¾éç¨äºæå è¿æµç¨çãåè½ä¸°å¯çé«éSerDes IPï¼åå©å¼åè è·å¾å¸åºç«äºä¼å¿ãéç¨5nm FinFETå·¥èºçDesignWare 112G以太ç½PHY IP解å³æ¹æ¡ï¼å ·æç¬ç¹çæ§è½ãè½èåé¢ç§¯ï¼è½å¤æ大å°èµè½å¼åè ï¼æ¾èéä½å ¶éæé£é©ï¼å¹¶æ´å¿«å®ç°æåã”

å

¶ä»èµæº

æå

³æ´å¤ä¿¡æ¯ï¼è¯·è®¿é®DesignWare 112G以太ç½PHY IPã

å

³äºDesignWare IP

æ°æç§ææ¯é¢åè¯ç设计æä¾é«è´¨éç¡

éªè¯IPæ ¸è§£å³æ¹æ¡çä¾åºåãDesignWare IPæ ¸ç»åå

æ¬é»è¾åºãåµå

¥å¼åå¨å¨ãåµå

¥å¼æµè¯ã模æIPãæ线åæ 线æ¥å£IPãå®å

¨IPãåµå

¥å¼å¤çå¨ååç³»ç»ã为äºå éåå设计ã软件å¼å以åå°IPæ´åè¿è¯çï¼æ°æç§æç“IP Accelerated计å”æä¾IPåå设计å¥ä»¶ãIP软件å¼åå¥ä»¶åIPåç³»ç»ãæ°æç§æå¨IPæ ¸è´¨éæ¹é¢ç广æ³æèµãå

¨é¢çææ¯æ¯æ以å强大çIPå¼åæ¹æ³ä½¿è®¾è®¡äººåè½å¤éä½éæé£é©ï¼å¹¶å å¿«ä¸å¸æ¶é´ãå询DesignWare IPæ ¸è¯¦æ

ï¼è¯·è®¿é®https://www.synopsys.com/designware-ipã

å

³äºæ°æç§æ

æ°æç§æï¼Synopsys, Inc., 纳æ¯è¾¾å

è¡ç¥¨ä»£ç ï¼SNPSï¼æ¯ä¼å¤åæ°åå

¬å¸çSilicon to Software™ï¼“è¯çå°è½¯ä»¶”ï¼åä½ä¼ä¼´ï¼è¿äºå

¬å¸è´åäºå¼åæ们æ¥å¸¸æä¾èµççµå产åå软件åºç¨ãä½ä¸ºä¸å®¶è¢«çº³å

¥æ æ®500å¼ºï¼ S&P 500 ï¼çå

¬å¸ï¼æ°æç§æé¿æ以æ¥ä¸ç´å¤äºå

¨ççµå设计èªå¨åï¼EDAï¼åå导ä½IP产ä¸çé¢å

å°ä½ï¼å¹¶æä¾ä¸çæ广æ³çåºç¨ç¨åºå®å

¨æµè¯å·¥å

·åæå¡ç»åãæ 论æ¨æ¯å建å

è¿å导ä½ççä¸ç³»ç»ï¼SoCï¼ç设计人åï¼è¿æ¯ç¼åéè¦æ´é«å®å

¨æ§åè´¨éçåºç¨ç¨åºç软件å¼å人åï¼æ°æç§æé½è½å¤æä¾æ¨çåæ°äº§åæéè¦ç解å³æ¹æ¡ãè¦è·ç¥æ´å¤ä¿¡æ¯ï¼è¯·è®¿é®www.synopsys.comã

Related Semiconductor IP

- 112G Ethernet PHY, TSMC N7 x4, North/South (vertical) poly orientation

- 112G Ethernet PHY, TSMC N7 x2, North/South (vertical) poly orientation

- 112G Ethernet PHY, TSMC N7 x1, North/South (vertical) poly orientation

- 112G Ethernet PHY, TSMC N6 x2, North/South (vertical) poly orientation

- 112G Ethernet PHY, TSMC N6 x1, North/South (vertical) poly orientation

Related News

- 新思科技推出业界首款连接大规模AI加速器集群的超以太网和UALink IP 解决方案

- 用于超大规模数据中心芯片的112G Ethernet PHY重磅发布,支持800G网络应用

- 智原提供联电40纳米以太网络GPHY IP授权服务

- Rambus面向网络和数据中心的微型芯片及共封装光学器件提供112G XSR / USR PHY,此解决方案适用于台积电7nm工艺上