智原FPGA-to-ASIC方案加速客户人工智能芯片技术革新

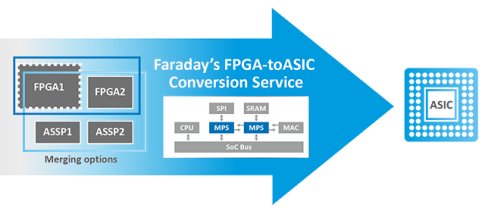

【台湾 新竹 】2018年3月12日 -- ASIC 设计服务暨IP研发销售厂商智原科技﹝Faraday Technology Corporation,TWSE:3035﹞今日宣布其FPGA-to-ASIC 解决方案已成功完成多项人工智能相关的ASIC 项目,如无人机图像识别、医疗图像分析、智能家电与3D感应等应用,提供了更优越的功耗与性能表现,同时降低整体系统成本。

智原的FPGA-to-ASIC 方案搭配其丰富的IP数据库,并提供先进FinFET工艺的PCIe Gen 3/4、MIPI D-PHY、DDR 3/4和SerDes 12/16/25/28/56Gbps等高速传输接口,可满足人工智能芯片对于高数据带宽与低延迟时间的需求。从云端到终端计算,无论机器视觉、自然语言处理(NLP)与情绪分析(sentiment analysis),智原都能依需求转换FPGA设计并整合所需IP,提供优化的ASIC 设计,相较于FPGA芯片,能源效率可提升30~100倍。

智原拥有25年的IP开发经验,可依据客户需求提供IP客制化服务,有效提高量产成本效益;其中智原的客制化SRAM面积可缩减约5%~50%,以及透过SRAM自动测试及修复的电路设计,芯片生产良率则可再向上提高达10%。

智原科技营运长林世钦表示:「随着AI算法规格趋向收敛,市场对AI产品需求量日益增加,客户陆续以芯片取代FPGA,以提升成本竞争力。智原的ASIC 服务迄今已完成数千个设计案,累积数亿颗芯片出货量,通过市场验证,可为客户降低整合风险与成本,加速实现新一代深度神经网络(DNN)算法应用。」

关于智原科技

智原科技(Faraday Technology Corporation, TWSE: 3035)为专用集成电路(ASIC)设计服务暨知识产权(IP)研发销售领导厂商,通过ISO 9001与ISO 26262认证,总公司位于台湾新竹科学园区,并于中国大陆、美国、日本与欧洲设有研发、营销据点。重要的IP产品包括:I/O、标准单元库、Memory Compiler、兼容ARM指令集CPU、DDR 2/3/4、低功耗DDR 1/2/3、MIPI、V-by-One、USB 3.X、10/100/1000 Ethernet、Serial ATA、PCI Express、可编程高速SerDes,以及数百个外设数字及混合讯号IP。更多信息,请浏览智原科技网站:www.faraday-tech.com

Related Semiconductor IP

- UCIe D2D Adapter & PHY Integrated IP

- Low Dropout (LDO) Regulator

- 16-Bit xSPI PSRAM PHY

- ASIL B Compliant MIPI CSI-2 CSE2 Security Module

- SHA-256 Secure Hash Algorithm IP Core

Related News

- 智原发布FPGA-Go-ASIC验证平台 加速FPGA转换ASIC

- 智原荣获ISO9001 Plus 品质知识典范奖,高经营品质打造设计服务

- 智原科技:全球第一家获颁ISO 26262证书的ASIC设计服务厂商

- 智原推出完整的FPGA转换ASIC方案