USB2.x OTG IIP

USB2.x OTG interface provides full support for the USB2.x synchronous serial interface, compatible with USB 2.0 specification.

Overview

USB2.x OTG interface provides full support for the USB2.x synchronous serial interface, compatible with USB 2.0 specification. Through its USB2.x compatibility, it provides a simple interface to a wide range of low-cost devices. USB2.x OTG IIP is proven in FPGA environment. The host interface of the USB2.x OTG can be simple interface or can be AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

USB2.x OTG IIP is supported natively in Verilog and VHDL

Key features

- Compliant with USB 2.0 specification.

- Compliant with USB 2.0 Enhanced Host Controller Interface (EHCI) Rev 1.0

- Asynchronous Park-mode

- Three caching models: no caching, micro-frame caching and frame caching

- NAK counter to limit unnecessary memory accesses

- Descriptor and data pre-fetch, pre-compute and cache

- Supports UTMI and ULPI transceivers.

- Operates at High-speed (480 Mbps), Full-speed (12 Mbps) and Low-speed (1.5 Mbps).

- Attach/detach, reset signaling and suspend/resume.

- Enumeration of low-speed, full-speed, and high-speed devices.

- All USB 1.1 transfer types are supported.

- Supports Interrupt/Bulk/Isochronous/Control Transfers.

- Supports High Bandwidth Interrupt and Isochronous endpoints.

- CRC16 checking and generation for HS/FS/LS data packets.

- CRC5 generation and checking for Tokens.

- Supports Split Transfers for FS/LS devices connected to HS Hubs while operating in Embedded Host Mode.

- Supports preamble for LS transfers while operating in Embedded Host Mode.

- Supports Protocol Layer Error Handling.

- Provides prioritized scheduling for periodic endpoints.

- Separate round robin scheduling algorithm within Periodic and Non-periodic endpoints pipes.

- Support LPM transactions.

- Support USB 2.0 Test mode.

- Configurable number of Downstream ports for Embedded Host Applications.

- Supports multiple devices connected under HS/FS hub for Embedded Host Applications.

- Supports USB Suspend state and supports remote wakeup devices.

- Supports all HS/FS USB Link Power Management States – L1, L2.

- Supports system low power and related system states such as Sleep, Hibernate, Warm/ Cold boot etc.

- Support for clock gating and multi-power-well support.

- Fully synthesizable.

- Static synchronous design.

- Positive edge clocking and no internal tri-states.

- Scan test ready.

- Simple interface allows easy connection to microprocessor/microcontroller devices

- This core achieves ASIL B and can be made to achieve ASIL D as per ISO26262

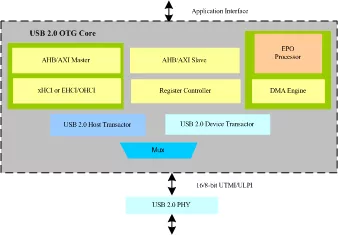

Block Diagram

Benefits

- Single Site license option is provided to companies designing in a single site.

- Multi Sites license option is provided to companies designing in multiple sites.

- Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

- Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

What’s Included?

- The USB2.x OTG interface is available in Source and netlist products.

- The Source product is delivered in verilog. If needed VHDL, SystemC code can also be provided.

- Easy to use Verilog Test Environment with Verilog Testcases

- Lint, CDC, Synthesis, Simulation Scripts with waiver files

- IP-XACT RDL generated address map

- Firmware code and Linux driver package

- Documentation contains User's Guide and Release notes.

- ISO26262 Safety Manual (SAM) Document

- ISO26262 Failure Modes, Effects and Diagnostics Analysis (FMEDA) Document

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about USB IP core

Exploring USB Applications and the Impact of USB IP

Understanding USB IP and Its Role in SOC Integration

What Designers Need to Know About USB Low-Power States

New USB 80Gbps Specification Boosts Data Rate, Enables Four Protocols on One Bus

New USB Device Class Specification Broadens Use Cases for I3C and I3C Basic

Frequently asked questions about USB IP cores

What is USB2.x OTG IIP?

USB2.x OTG IIP is a USB IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this USB?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this USB IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.