UDP/IP Offload Engine - 10G/25G/40G/100Gbit/s Ethernet UDP/IP

Fast, customizable data transfer supported by expert engineering and design services to optimize the performance of your product.

Overview

Fast, customizable data transfer supported by expert engineering and design services to optimize the performance of your product.

User Datagram Protocol (UDP/IP) is a communications protocol used for establishing connections between applications on the Internet. The UDP Protocol is a transport layer that runs on top of the Internet Protocol (IP) Layer and is used for connections where high sustained throughput is a priority and some data loss is expected, such as with video and audio streaming. Chevin Technology’s 10G /25G/40G/100G UDP Ethernet IP core for FPGAs has low latency and bandwidth overhead, as it sends packets of data without confirming receipt. De-fragmentation is available as an option, so large UDP datagrams can be easily sent and received. The UDP IP core provides individual port numbers to differentiate between user requests, and receipt of data is verified using the checksum functionality.

The 10G /25G/40G/100G UDP Ethernet IP core is configurable for Intel & AMD Xilinx FPGAs and simplifies integration by handling the complete Ethernet frame assembly.

The UDP IP core is a mature IP core with proven success in customers’ projects. Reference designs are available for various boards to assist with integration and we offer our customers bespoke, expert engineering support packages to help meet their project goals.

A simple AXI4 streaming interface is all that is required to start sending and receiving UDP datagrams, and only the user data payload is exchanged between the application and the UDP core. For a single port application the port number can be set to a constant, hard coded or software configurable. A multi-port application is supported by a single UDP IP core by using the TDEST sideband embedded in the streaming interface.

Key features

- AXI4s MAC & Application Interfaces

- De-fragmentation option available

- Designed to UDP specification RFC768

- Compose/Decompose complete UDP Datagrams

- IP frame Checksum Generator/Checker

- Jumbo frame support up to 32k

- Configurable operation port filtering

- 1-64k Ports (configurable ports & filters)

- Detailed traffic analysis statistics collection

- ARP/ICMP layers for complete FPGA hosted application with ARP and ICMP “ping”

- Integrated Streaming FIFO – 4 Block RAMs

- Flow Control between MAC/User logic

- Consistently low and predictable latency with zero frame jitter

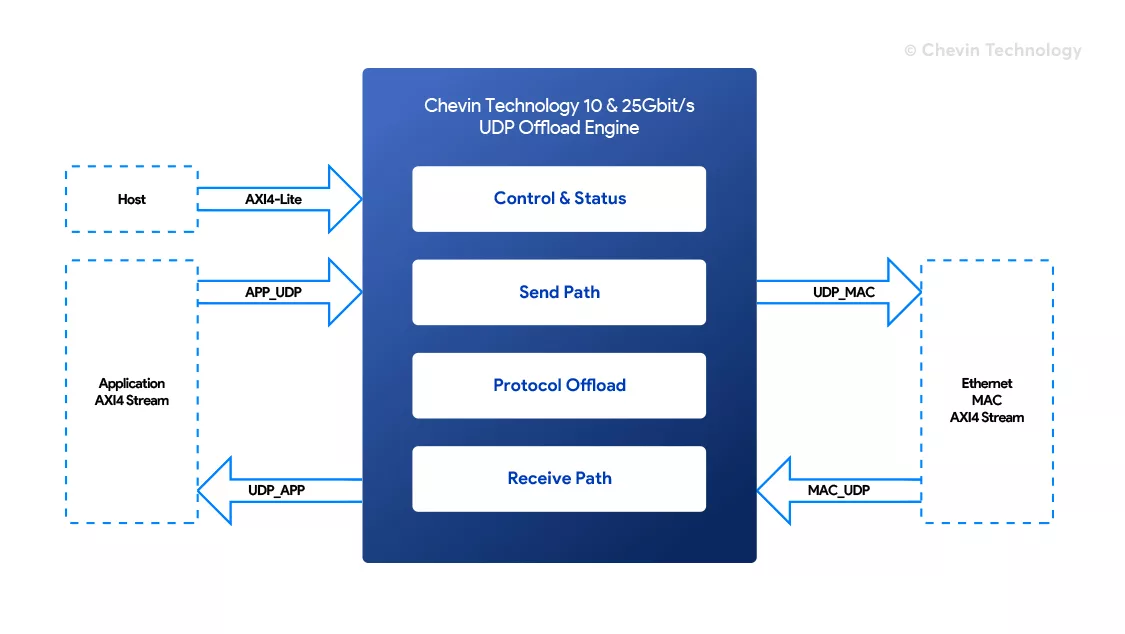

Block Diagram

Benefits

- Chevin Technology’s 10/25/40/100G UDP Ethernet IP is FPGA Synthesisable EndPoint with Checksum Offload for ultra low-latency connectivity.

- The 10/25/40/100G UDP IP cores simplify FPGA integration of an ultra fast UDP/IP layer in any FPGA by handling the complete Ethernet frame assembly.

- A simple AXI4 streaming interface is all that is required to start sending and receiving UDP datagrams, and only the “user data” payload is exchanged between the application and the UDP block. For a single port application the port number can be set to a constant, hard coded or software configurable. A multi- port application is supported by a single UDP IP core by using the udp port sideband embedded in the streaming interface.

Applications

- Artificial Intelligence

- Machine Learning

- Video Imaging

- Image/Signal Processing

- Internet Security Monitoring

- Data Storage & Capture Systems

- Trade Execution & monitoring

- HPC/ Big Data systems

- Data Mining

What’s Included?

- Encrypted compiled netlist

- Datasheet & User Guide

- Reference Designs

- Simulation Test bench

- Build scripts for Vivado, Quartus

- Support for integration into FPGA

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is UDP/IP Offload Engine - 10G/25G/40G/100Gbit/s Ethernet UDP/IP?

UDP/IP Offload Engine - 10G/25G/40G/100Gbit/s Ethernet UDP/IP is a Ethernet IP core from Chevin Technology Limited listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.