UCIe D2D Adapter & PHY Integrated IP

A UCIe solution ready to support any protocol layer The D2D Adapter for UCIe combined with the UCIe PHY from a UCIe solution read…

Overview

A complete UCIe solution ready to support any protocol layer

The D2D Adapter for UCIe combined with the UCIe PHY from a complete UCIe solution ready to support any protocol layer. The offering consists of two IP parts the D2D adapter from Chip Interfaces and the UCIe PHY from Extoll. Chip Interfaces and Extoll collaborate on UCIe technology to create a complete solution for our customers.

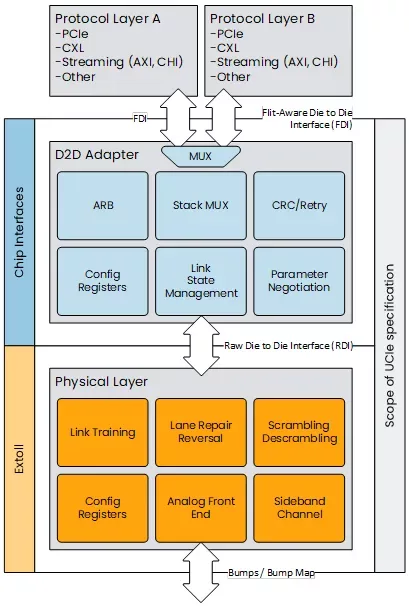

The combined solution connects the Flit Aware D2D Interface (FDI) directly to bumps on the die. EXTOLL’s PHY IP supports the standard package which is specifically designed to enable cost-effective packages based on organic substrates. Independent of the package type, the UCIe standard defines functions and features (mandatory and optional) and according blocks that enable them for compliance and interoperability. The major top-level functions both for the PHY and the D2D Adapter are illustrated in the figure below.

EXTOLL’s high-speed UCIe PHY IP provides low-latency, high-bandwidth serial I/O capabilities for state-of-the-art Chiplet projects to support a wide range of applications in Networking, HPC/AI, QC, Aerospace/Defense, and Automotive/Industrial segments. The PHY comes as a 16-lane bidirectional macro and one common PLL that can be driven at various input reference clock frequencies to achieve line rates from 4 to 16 Gbps. The PHY provides a constant low latency to support deterministic latency operations. Critical blocks benefit from EXTOLL´s industry-leading SerDes architecture and products, that are optimized for highest performance and power efficiency. The PHY consists of TX, RX for the Mainband, the Sideband, PLL and all required control logic.

Chip Interfaces D2D Adapter is a scalable adapter layer between one or more protocol components and the UCIe PHY, which ensures efficient data transfer across the UCIe Link by seamlessly coordinating with the Protocol Layer and Physical Layer. By minimizing logic on the main data path, it delivers a low-latency, optimized pathway for protocol Flits. When handling CXL protocol, the D2D Adapter incorporates ARB/MUX functionality to support multiple simultaneous protocols. For scenarios where the Raw BER exceeds 1e-27, it implements the CRC and Retry scheme defined in the UCIe Specification, ensuring reliable data transport for PCIe, CXL, or other protocols including Streaming protocols. Additionally, the D2D Adapter manages critical functions such as higher-level Link state machine coordination, parameter exchanges with remote Link partners for protocol options, and power management synchronization when supported.

Both IP core forming the combined package have been thoroughly tested using advanced verification and modeling using Universal Verification Methodology (UVM) and System Verilog random regression environments. They fully reflect the requirements of the UCIe Standard.

The full IP package is available for licensing and complete delivery now.

Block Diagram

Benefits

- Interoperability Tested: Chip Interfaces Digital IPs, seamlessly interoperable with all leading PHY providers, saves you time and resources. No more compatibility concerns.

- Faster time to Market: Chip Interfaces IP cores seamlessly integrate into your projects, saving you time and resources. Full feature testing across multiple tape-outs guarantees rock-solid reliability and peace of mind.

- Quality guaranteed: Chip Interfaces IP cores undergo rigorous UVM regression testing for comprehensive functional coverage, lint and CDC checks for rock-solid design, and exhaustive HW tests to guarantee flawless performance.

- Reduced Total cost: Chip Interfaces IP cores are proven & pre-tested, slashing integration time and thereby lowering total project costs.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UCIe IP core

Synopsys Advances Die‑to‑Die Connectivity with 64G UCIe IP Tape‑Out

Cadence Tapes Out 32GT/s UCIe IP Subsystem on Samsung 4nm Technology

The Next-Generation UCIe IP Subsystem for Advanced Package Designs

Cadence Silicon Success of UCIe IP on Samsung Foundry’s 5nm Automotive Process

40G UCIe IP Advantages for AI Applications

Frequently asked questions about UCIe IP cores

What is UCIe D2D Adapter & PHY Integrated IP?

UCIe D2D Adapter & PHY Integrated IP is a UCIe IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this UCIe?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UCIe IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.