Overview

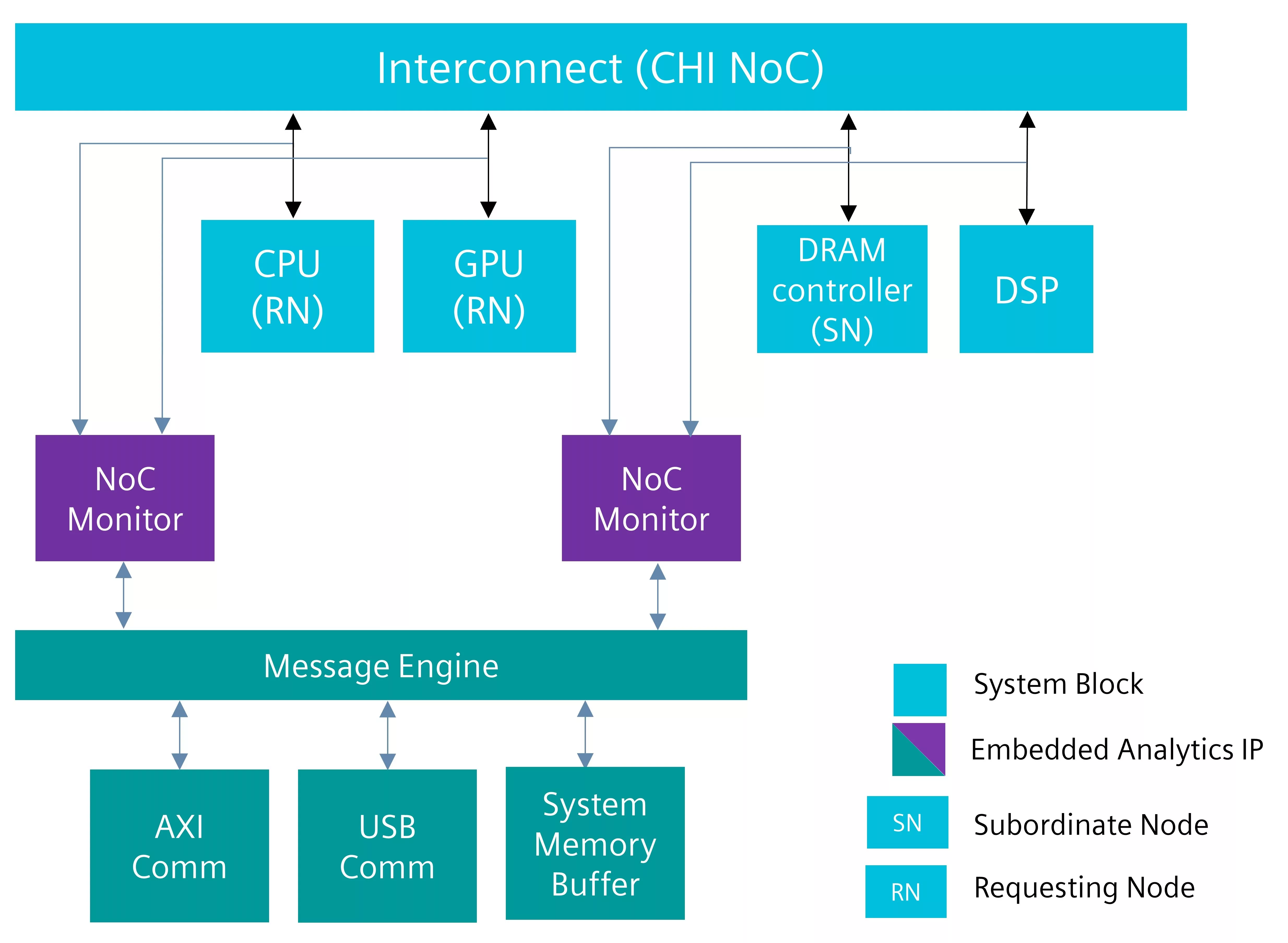

The Tessent Embedded Analytics NoC Monitor provides non-intrusive monitoring of interconnect activity across the AMBA 5 CHI (Coherent Hub Interface) network-on-chip (NoC).

The NoC Monitor enables full transaction-level visibility of traffic with a wide range of measurements, analytics and statistics gathering. All of these are run-time configurable and include “logic analyzer” style controls and dependencies, local buffering and cross-triggering. The modules can track transactions (e.g. trace) and automatically gather statistics to identify issues such as contention, peak traffic, and deadlock. It is the market’s most comprehensive CHI debug solution.

All Tessent Embedded Analytics monitors (IPs), can be accessed via a dedicated, secure communication infrastructure. Non-intrusive debug and monitoring using an off-chip host or debugger is facilitated through USB 2, USB 3, JTAG, or Aurora interfaces. Embedded software can drive the system via an AXI interface to create a self-contained on-chip monitoring system.

Learn more about Network-On-Chip IP core

Ensuring Network-on-Chip (NoC) security is crucial to design trustworthy NoC-based System-on-Chip (SoC) architectures. While there are various threats that exploit on-chip communication vulnerabilities, eavesdropping attacks via malicious nodes are among the most common and stealthy. Although encryption can secure packets for confidentiality, it may introduce unacceptable overhead for resource-constrained SoCs.

Microcontrollers (MCUs) are no longer the humble workhorses of embedded systems. Today’s MCUs rapidly evolve into compact, high-performance computing platforms, integrating artificial intelligence (AI), advanced security features, and real-time processing into power-constrained environments.

In this article, we will dive deeper into a comprehensive methodology for formally verifying an NoC, showcasing the approaches and techniques that ensure our NoC designs are robust, efficient, and ready to meet the challenges of modern computing environments.

Many people have heard the term cache coherency without fully understanding the considerations in the context of system-on-chip (SoC) devices, especially those using a network-on-chip (NoC). To understand the issues at hand, it’s first necessary to understand the role of cache in the memory hierarchy.

In the world of system-on-chip (SoC) devices, architects encounter many options when configuring the processor subsystem. Choices range from single processor cores to clusters to multiple core clusters that are predominantly heterogeneous but occasionally homogeneous.

Today’s complex system-on-chip (SoC) designs can contain between tens to hundreds of IP blocks. Each IP block may have its own data width and clock frequency and employ one of the standard SoC interface protocols: OCP, APB, AHB, AXI, STBus, and DTL. Connecting all these IPs is a significant challenge.