FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults.

For complex SoCs in process nodes, CPU duplication and memory protection logic are no longer sufficient to address all the metric…

Overview

For complex SoCs in advanced process nodes, CPU duplication and memory protection logic are no longer sufficient to address all the metrics required to meet the more stringent ISO 26262 ASIL and IEC 61508 SIL levels.

Implementing functional safety and data protection features in hardware is easier and less risky than software-only implementations.

Key features

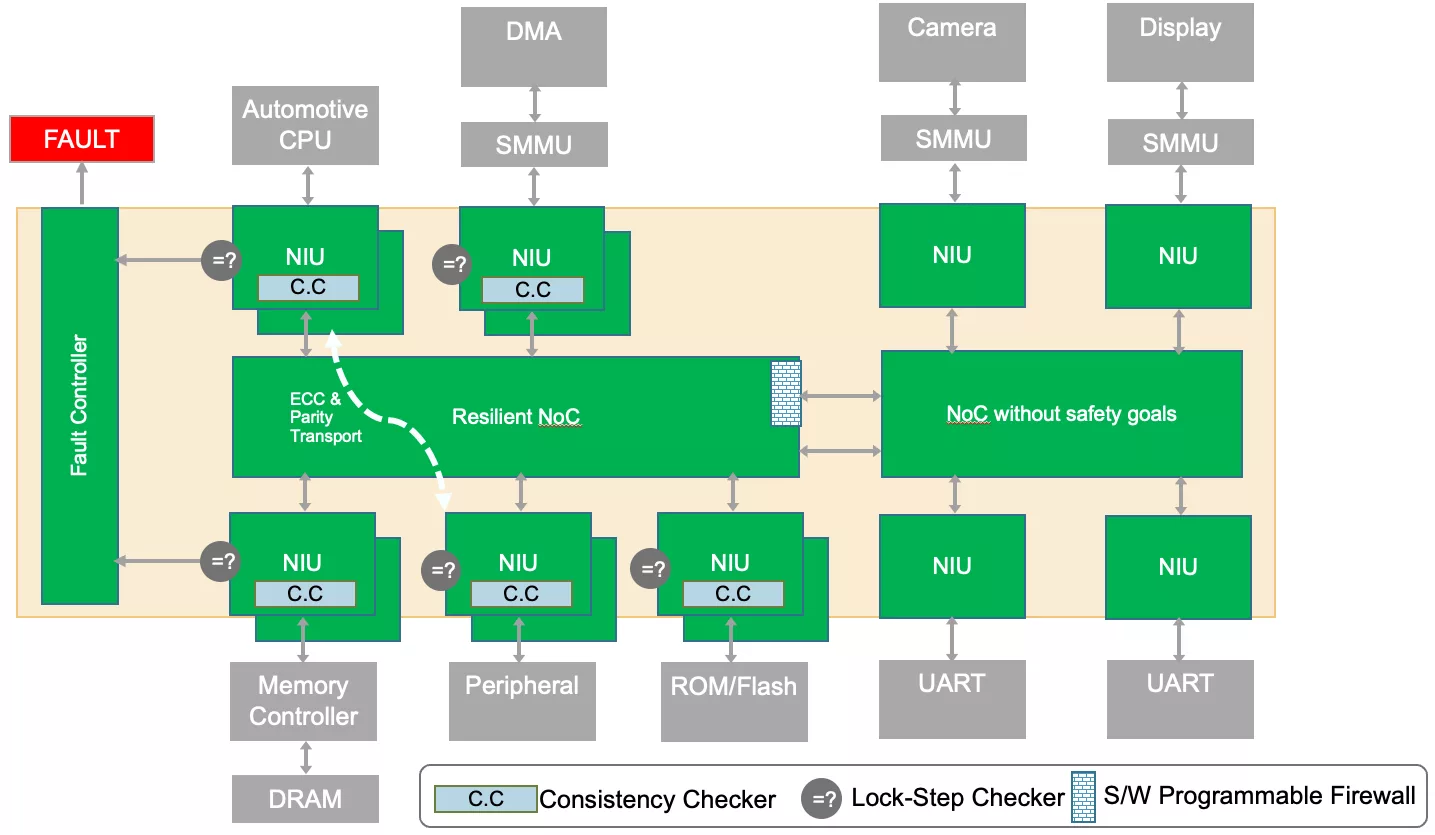

- Data protection through ECC and parity checking

- Out-of-the-box support for ARM Cortex-R Processors

- Port Checking

- Unit protection by duplication and redundancy

- Similar to dual-core lockstep (DCLS) and often required for ASIL C or D systems as specified in the automotive ISO 26262 standard

- Duplicate unit checkers and fault safety controller

- Built in Self-Test (BIST) for resilience functions

- Data protection by monitoring

- Data packet integrity checkers

- Easy partitioning of any SoC into resilient and non-resilient domains.

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults.?

FlexNoC Functional Safety (FuSa) Option helps meet up to ISO 26262 ASIL B and D requirements against random hardware faults. is a Network-On-Chip IP core from Arteris listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.