High speed NoC (Network On-Chip) Interconnect IP

The ORBIT On-Chip Interconnect (OIC) delivers exceptional performance, and SoC design flexibility based on automated end-to-end i…

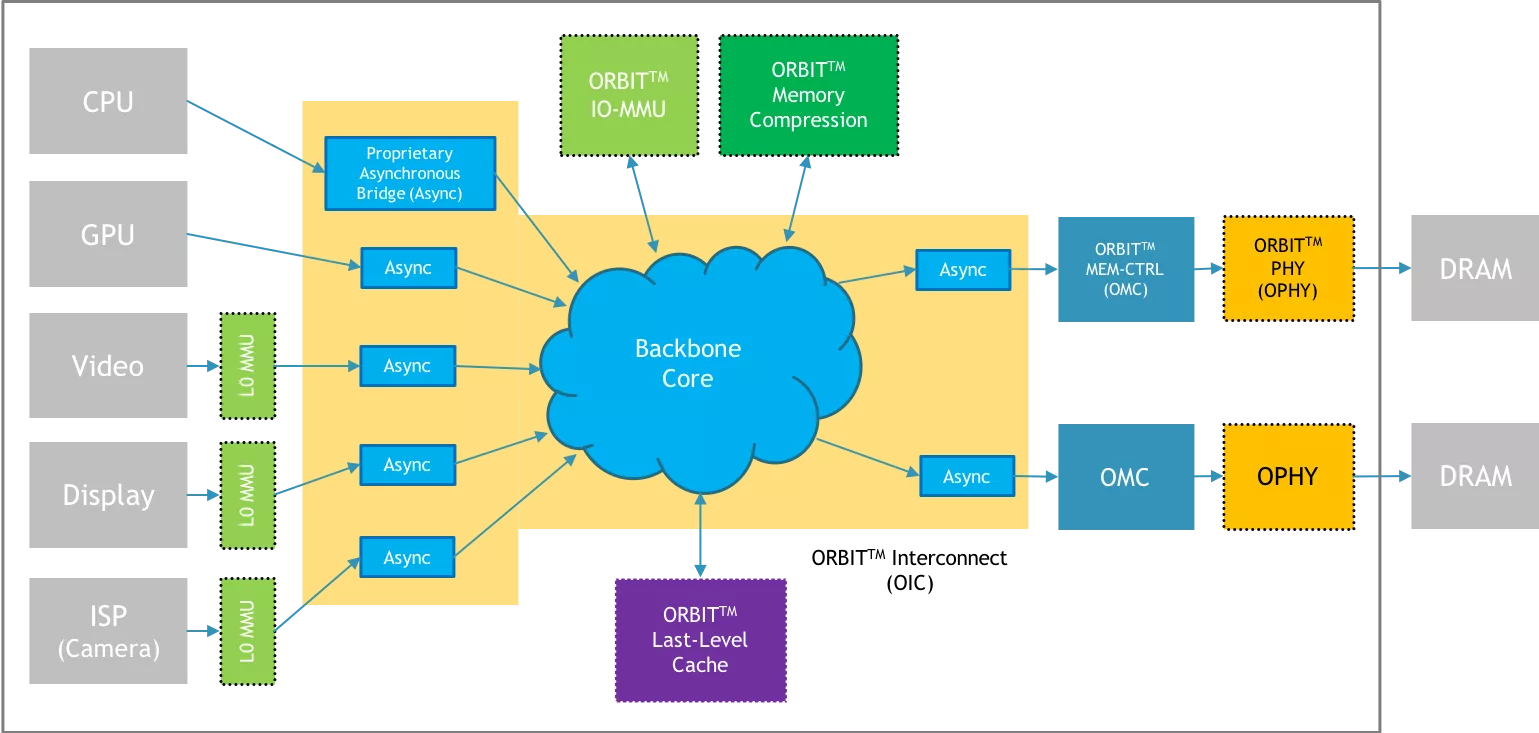

Overview

The ORBIT On-Chip Interconnect (OIC) delivers exceptional performance, and SoC design flexibility based on automated end-to-end interconnect generation flow. It enables high-speed routing with pre-calculated routing path details and supports higher speed, low latency, and floorplan flexibility.

Key features

- Memory Subsystem IP

- Tuning the performance for the entire SoC memory subsystem

- ActiveQoS bandwidth and latency control for the entire SoC memory subsystem

- High-Speed HyperPath Technology

- More than 1GHz at 28nm processor or more than 800MHz at low power 28nm

- Flexible Floorplan & Physical Design Friendly

- Long-distance Asynchronous Bridge (LDA) technology solves long and narrow topology design

- Ultra Low Power

- Enables <200uW idle power for entire backbone (+3M gate size)

- Area (Wire Congestion)

- Less than 50% of typical AXI-based backbone bus area

- Design Tools

- End-to-end RTL and verification package generation with ORBIT toolkit

Block Diagram

Benefits

- High Performance

- Proprietary HyperPath technology enabling 2x performance

- Extremely low latency with LDA technology

- Dynamic priority control in OIC and OMC, based on observed latency & bandwidth (ActiveQoS)

- Low Power Consumption

- Advanced Clocking enables extremely low power

- Proactively clock-gating

- High Flexibility

- Automated end-to-end RTL generation with an ORBIT design toolkit

- Fast & easy SoC design of high-speed and long-distance interconnect

- Safety & Security

- End-to-end ECC (SECDED) support

- End-to-end at-speed BIST

Applications

- Automotive,

- Application Processors,

- Digital Baseband Modems,

- Set-Top-Box,

- Digital TV,

- OTT,

- Surveillance,

- IoT,

- Enterprise SSD Controllers

What’s Included?

- IP Core RTL

- Simulation Environment

- Synthesis, Lint Script

- Detail Documentation

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is High speed NoC (Network On-Chip) Interconnect IP?

High speed NoC (Network On-Chip) Interconnect IP is a Network-On-Chip IP core from OPENEDGES Technology, Inc. listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.