AHB Multi Fabric

The AHB Fabric provides the necessary infrastructure to connect up to 16 shared AHB Slaves to up to 16 AHB-Lite Bus Masters.

Overview

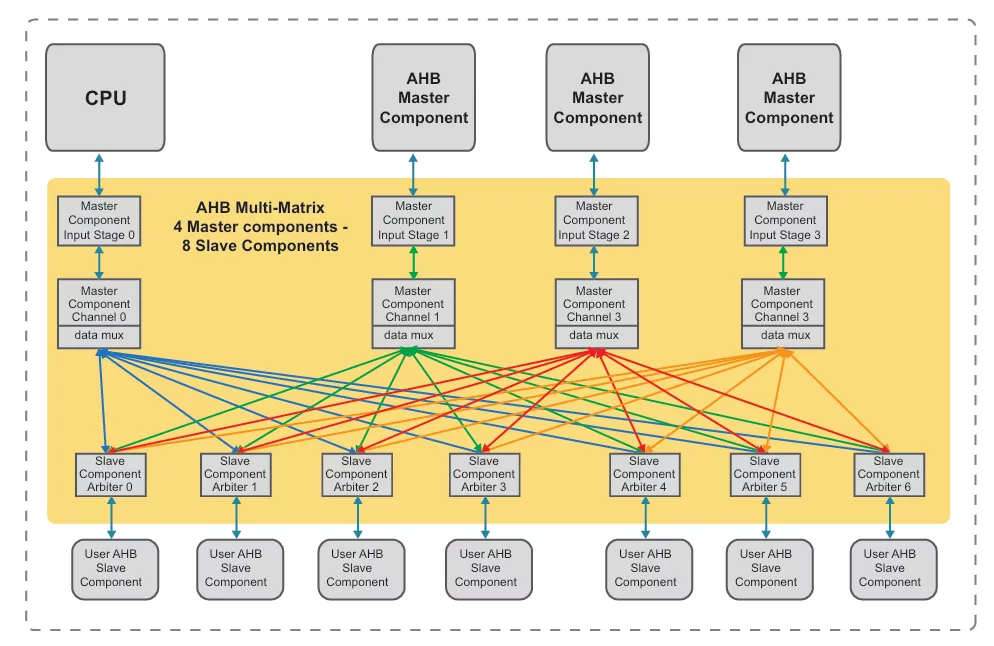

The AHB Fabric provides the necessary infrastructure to connect up to 16 shared AHB Slaves to up to 16 AHB-Lite Bus Masters. The off-the-self configuration support 4 AHB Masters and 7 AHB Slaves and includes a remapping selection.

In a typical AHB system, several AHB Masters may compete for a shared (AHB) bus; a bus arbiter determines bus ownership. The AHB Fabric allows for the various AHB-Lite Masters to connect to several different shared peripherals without the need to arbitrate for a shared AHB bus. Instead, arbitration is performed at the peripheral. This way, the various Masters may see a significant increase in performance over a standard AHB system. However, systems where multiple masters need frequent access to the SAME peripheral will see only a modest performance increase.

The Fabric may be connected to the remainder of the subsystem as follows. Each of the AHB Fabric’s M Mirrored Slave Ports is connected to an AHB Slave module (e.g. External Bus Interface, Memory Controller, AHB-to-APB Bridge). On the Master side, each of the N-1 AHB Fabric’s Mirrored Master Ports is connected to either the output side of an AHB Arbiter (in the case where each AHB system has multiple bus Masters) or directly to an AHB or AHB-Lite Master such as a microprocessor.

Key features

- AMBA® 2.0 Compatible

- Multiple AHB Channels

- Off the shelf core supports 4 Masters and up 7 Slaves

- Arbitration is done at each slave

- Other configurations are available

Block Diagram

What’s Included?

- Verilog Source

- Complete Test Environment

- AHB Bus Functional Model

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is AHB Multi Fabric?

AHB Multi Fabric is a Network-On-Chip IP core from Silvaco, Inc. listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.