Simulation VIP for SPDIF

Incorporating the latest protocol updates, the mature and comprehensive Cadence® Verification IP (VIP) for the SPDIF protocol pro…

Overview

Incorporating the latest protocol updates, the mature and comprehensive Cadence® Verification IP (VIP) for the SPDIF protocol provides a complete bus functional model (BFM), integrated automatic protocol checks, coverage model, and compliance tests. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for SPDIF helps you reduce time to test, accelerate verification closure, and ensure end-product quality. Our VIP runs on all major simulators and supports SystemVerilog and e verification languages along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported Specification: Indian Standard DIGITAL AUDIO INTERFACE PART 3 CONSUMER APPLICATIONS (IEC 60958-1)

Key features

- Maximum Audio Sample Word Length

- Supports both 20-bit and 24-bit audio word length format. In 20-bit audio word length format, AUX field will be present

- Audio Sample Word Length

- Supports padding in audio data if audio sample word length is less than the maximum audio word length

- Parity Generation

- Generates parity internally

- Preamble Error Injection

- Transmits erroneous preamble

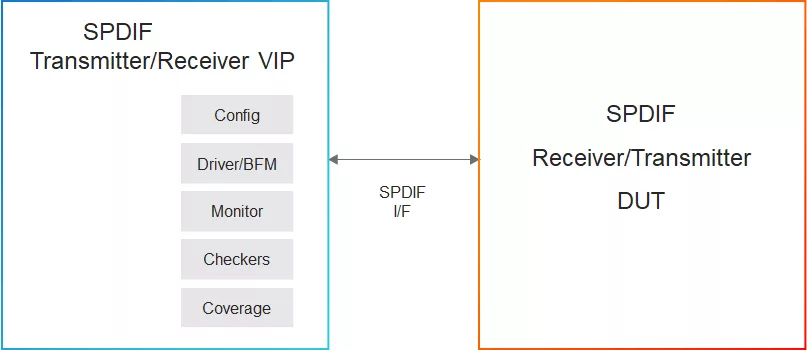

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPDIF IP core

A configurable FPGA-based multi-channel high-definition Video Processing Platform

Using FPGAs to interface with digital communication protocols

Optimizing the Implementation of Dolby Digital Plus in SoC Designs

One Approach to IP Cores: Ten Years and Going Strong

Timing key to optimizing audio performance in consumer products

Frequently asked questions about S/PDIF IP cores

What is Simulation VIP for SPDIF?

Simulation VIP for SPDIF is a SPDIF IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SPDIF?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPDIF IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.