SPDIF (IEC60958) Verification IP

SPDIF Verification IP provides an smart way to verify the SPDIF component of a SOC or a ASIC.

Overview

SPDIF Verification IP provides an smart way to verify the SPDIF component of a SOC or a ASIC. The SmartDV's SPDIF Verification IP is fully compliant with IEC 60958 Specification and provides the following features.

SPDIF (IEC60958) Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

SPDIF (IEC60958) Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Full SPDIF functionality as per specs IEC 60958 and IEC 61937.

- Supports SMPTE 337M standards for non Linear PCM Audio

- Supports AES/EBU, AES3 standards for Linear PCM Audio

- Supports following sampling/Driving rates,

- 32 kHz

- 44.1 kHz

- 48 kHz

- 22.05 kHz

- 24 kHz

- 768 kHz

- 384 kHz

- 352.8 kHz

- 1536 kHz

- 88.2 kHz

- 96 kHz

- 176.4 kHz

- 192 kHz

- Supports 32 audio channels.

- Supports configurable Baud rate control.

- Supports the Biphase-mark code.

- Supports start bit correction.

- Supports clock recovery Circuit.

- Supports injection of various errors

- Preamble error

- Channel status error

- Parity Error

- Various field errors

- Notifies the testbench of significant events such as transactions, warnings, and protocol violations.

- Supports constraints Randomization.

- Callbacks in transmitter, receiver and monitor for user processing of data.

- Functional coverage for complete SPDIF IEC 60958 and IEC 61937 features.

- SPDIF Verification IP comes with complete testsuite to verify each and every feature of SPDIF specification.

- Status counters for various events on bus.

- On-the-fly protocol and data checking

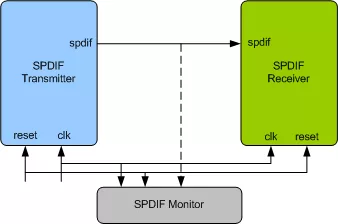

Block Diagram

Benefits

- Faster testbench development and more complete verification of SPDIF designs.

- Easy to use command interface simplifies testbench control and configuration of TX and RX.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the SPDIF testcases.

- Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SPDIF IP core

A configurable FPGA-based multi-channel high-definition Video Processing Platform

Using FPGAs to interface with digital communication protocols

Optimizing the Implementation of Dolby Digital Plus in SoC Designs

One Approach to IP Cores: Ten Years and Going Strong

Timing key to optimizing audio performance in consumer products

Frequently asked questions about S/PDIF IP cores

What is SPDIF (IEC60958) Verification IP?

SPDIF (IEC60958) Verification IP is a SPDIF IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SPDIF?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPDIF IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.