Simulation VIP for SAS

The Cadence® Verification IP (VIP) for SAS is part of Cadence’s broad storage interface verification IP (VIP) portfolio.

Overview

The Cadence® Verification IP (VIP) for SAS is part of Cadence’s broad storage interface verification IP (VIP) portfolio. Serial Attached SCSI (SAS) has been the interface of choice for mission-critical enterprise storage subsystems, with the next-generation SAS 24G addressing the transmission and storage of data growing at an exponential rate due to an increasingly connected world. As a part of Cadence’s datacenter and cloud solution, the VIP for SAS delivers a comprehensive solution that was delivered ahead of the 2017 SAS plug-festival. Built on top of an industry-known and proven platform that was designed for easy integration in testbenches at the IP, system-on-chip (SoC), and system level, the SAS VIP runs on all simulators and supports SystemVerilog along with the widely adopted Universal Verification Methodology (UVM). This enables verification teams to reduce time spent on environment development, and redirect the saved time to cover a larger verification space, accelerate verification closure, and ensure end-product quality.

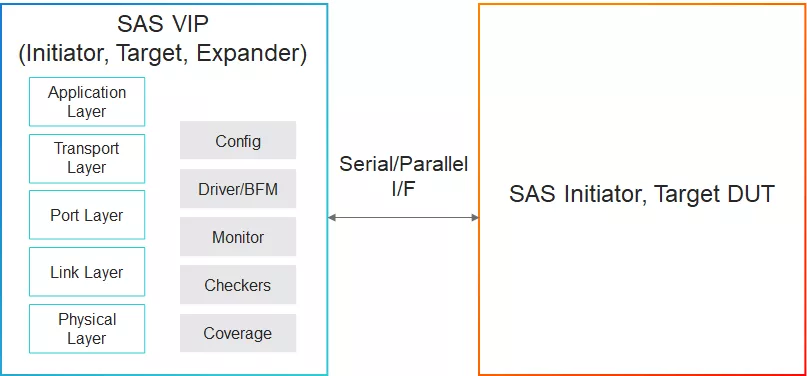

The Cadence SAS VIP is a complete verification solution that includes a complete bus functional model (BFM), integrated protocol checks, coverage model, a rich set of error injection capabilities, and compliance tests. Supporting all previous SAS generation data rates (1.5G, 3G, 6G, and 12G) along with all application-level protocols (SSP, SMP, STP), the VIP for SAS allows users to verify all SAS device configurations (initiator, target, and expander). With a layered architecture and powerful callback mechanism, verification engineers can verify SAS features at each functional layer (Phy, link, transport, and application layer) and create highly targeted designs while taking advantage of the latest design methodologies for random testing to cover a larger verification space.

Supported specification: SPL-4 specification.

Key features

- Device type

- Initiator, Target, and Expander

- Operating Modes

- Supports all SAS speeds: 1.5, 3, 6, 12, 24Gb/s

- DWORD mode: 12Gb/s and lower

- Packet mode: 24Gb/s and greater

- Interface Support

- Serial: DWORD and Packet mode

- Parallel: DWORD mode: 10 bit, 16 bit, 32 bit, 40 bit and Packet mode: 32 bit, 128 bit

- Transport Layer Protocols

- SSP, SMP, and STP

- Expander Support

- Configurable support for 2 to 128 external expander ports

- Each port can operate at different speeds

- ECN, ECR, BPP support

- Narrow and Wide Port Support

- Narrow with One PHY in the port and Wide with more than one PHY per port

- PHY Power Conditions

- Support of PHY low-power conditions and sequences

- PHY Reset Sequences

- OOB sequence, speed negotiation sequence generation and verification at all data rates

- Active PHY Transmitter Adjustment

- Support for APTA in packet mode

- Persistent Connection

- Supports persistent connection in SSP connection

- Primitives

- Support for complete set of primitives: generation and verification

- Logical Links

- Support for multiplexing of logical links

- Broadcast

- Support for all broadcast types

- Frame Support

- Supports for all frames: Generation and verification

- Bypass Capabilities

- OOB, Speed Negotiation, Training, and Scrambler

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SAS IP core

Video: Cadence Demonstrates PCIe Gen3 Silicon at PCI-SIG Dev-Con (SAS RAID Controller)

Embedded Security explained: IPsec and IKEv2 for embedded Systems

ReGate: Enabling Power Gating in Neural Processing Units

Bringing IPsec into the Quantum Safe Era

The Benefits of a Multi-Protocol PMA

Frequently asked questions about SAS IP cores

What is Simulation VIP for SAS?

Simulation VIP for SAS is a SAS IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this SAS?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SAS IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.