SAS Synthesizable Transactor

The SAS Synthesizable Transactor verifies SAS interfaces of designs SAS Interface.

Overview

The SAS Synthesizable Transactor verifies SAS interfaces of designs SAS Interface. SAS is build on top of it to make it robust. SAS Synthesizable Transactor provides a smart way to verify the SAS component of a SOC or a ASIC in Emulator or FPGA platform. SAS Synthesizable Transactor is developed by experts in networking, who have developed networking products in companies like Intel, Cortina-Systems, Emulex, Cisco. We know what it takes to verify a networking product. The SmartDV's SAS Synthesizable Transactor is fully compliant with SAS 2.1, SAS 3.0, SAS 4.0,SAS 5.0, SAS Protocol Layer SPL 1.0, SPL 2.0, SPL 3.0, SPL 4.0 and SPL 5.0 of the SAS Specification and provides the following features.

Key features

- Supports trained 1.5,3,6,12 and 22.5 Gbps speeds.

- Supports untrained 1.5,3 and 6 Gbps speeds.

- Supports Narrow ports and wide ports.

- Supports Reset sequences

- Supports Expander device model function.

- Supports Retimer device model

- Supports Discover process

- Supports Phy power conditions

- Supports Successful low phy power conditions handshake sequence.

- Supports SATA Spin-up and Port Selectors.

- Supports SAS Dword mode and Packet mode.

- Complete Disparity checking.

- Complete Kcode & Dcode validity and alignment.

- Complete 8b/10b Encode and Decode functions.

- Complete 8b/10b encoding and decoding, Error injection.

- Complete Controls to inject bit errors.

- Supports OOB sequence generation and checking.

- Configurable OOB signals and speed of operation.

- Configurable phy layer timers.

- Supports BMC Encoding.

- Supports Forward error correction encoding & decoding.

- Supports Interleaved SPL Packet mode encoding & decoding.

- Supports SNW-3 Phy capabilities bits.

- Supports Spread Spectrum Clocking Modulation techniques.

- Supports Expander device handling of connection.

- Supports Phy reset sequences.

- Supports SAS speed negotiation sequence

- Supports Train_Tx-SNW & Train_Rx-SNW for SAS Dword mode and Packet mode.

- Complete dword synchronization,SPL packet synchronization and resynchronization phy layer state machines

- Complete transmitter training and active phy transmitter adjustment phy layer state machines

- Supports Management application client model for APTA.

- Supports Primitive encoding, binary primitive coding, and extended binary primitive coding.

- Supports Physical link rate tolerance management

- Supports Bit order of CRC and scrambler for SAS Dword mode and Packet mode.

- Supports Address frames

- Supports Link reset sequence

- Supports Entering a low phy power condition

- Supports STP,SSP& SMP Link layer Connections.

- Supports link layer Rate matching for SAS Dword mode and Packet mode.

- Supports SAS domain changes

- Complete power control,identification and hard reset link layer state machines

- Complete SAS logical phys,expander logical phys,SSP,STP and SMP link layer state machines

- Supports configurable for port control mode page

- Supports SSP frame fields

- Supports STP frame fields

- Supports SMP frame fields

- Complete overall control and phy control state machine

- Supports SSP,STP and SMP frame fields errors

- Supports SCSI,ATA and management frame transaction

- Supports Parameter Storage, Mode Pages and Log Pages.

- Selectable Primitive CONT and fill substitution processing.

- Configurable Receive and Transmit fifo latencies.

- User defined primitive transmission.

- Single or multi-bit error injection.

- User defined primitives & frame transmission.

- Randomized/directed CRC error injection and checking.

- Ability to enable/disable scrambling on the fly.

- Supports LBA with HDD size configuration.

- APIs providing backdoor access to HDD.

- Programmable auto-activate support using configuration.

- Supports standard SCSI commands.

- Supports standard SMP commands.

- Supports standard STP commands.

- Supports Expander device model features & Expander device handling of connections.

- Supports Zone permission configuration.

- Supports STP flow control.

- Configurable FIS latencies, FIFO depths and FIS size.

- Software Settings Preservation and Hardware Feature Control support.

- Supports the Non 512 Byte Sector Size.

- Supports HDD activity activation.

- Ability to Automatic Partial to Slumber Transitions.

- Supports DHU Specific Operation.

- Rebuild Assist is supported.

- Enabled Hybrid Information Feature.

- Device Signature return Feature.

- Supports SATA features.

- Functional coverage for complete SAS features.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- SAS Synthesizable Transactor comes with complete testsuite to test every feature of SAS specification.

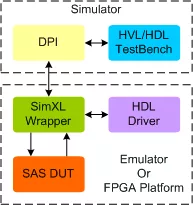

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the SAS testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about SAS IP core

Video: Cadence Demonstrates PCIe Gen3 Silicon at PCI-SIG Dev-Con (SAS RAID Controller)

Embedded Security explained: IPsec and IKEv2 for embedded Systems

ReGate: Enabling Power Gating in Neural Processing Units

Bringing IPsec into the Quantum Safe Era

The Benefits of a Multi-Protocol PMA

Frequently asked questions about SAS IP cores

What is SAS Synthesizable Transactor?

SAS Synthesizable Transactor is a SAS IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this SAS?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SAS IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.