Simulation VIP for PLB

In production since 2011.

Overview

In production since 2011.

This Cadence® Verification IP (VIP) supports the IBM PLB standard. It provides a mature, highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms, making it applicable to intellectual property (IP), system-on-chip (SoC), and system-level verification. The VIP for PLB is compatible with the industry-standard Universal Verification Methodology (UVM), runs on all leading simulators, and leverages the industry-standard Cadence Memory Model core architecture, interface, and use model. The PLB VIP supports DCR, PLB4, and PLB6, for core, devices, and bus controller.

Supported specification: PLB4 and PLB6 Specifications - IBM confidential.

Key features

- Protocol

- Command, read data, and write data buses - DCR, PLB4, PLB6

- Interface

- Core, device, snooper pin, and snoopable and non-snoopable commands - PLB4, PLB6

- Address ordering

- Address overlapping read/write - PLB4, PLB6

- Cache coherency

- Cache coherency for snoopers - PLB6

- Data transfer

- Supports bytes, half-word, word, or line/burst transfer - PLB4, PLB6

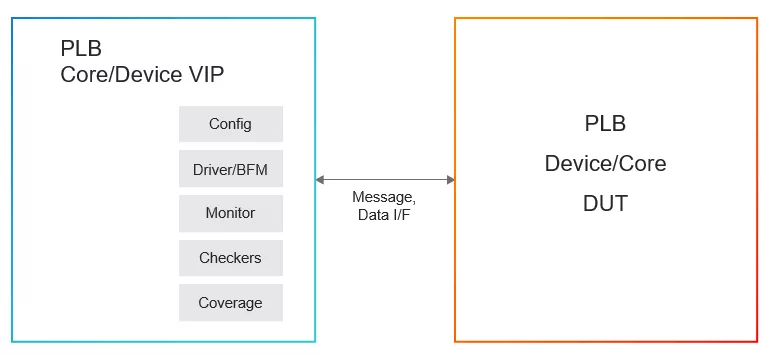

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Simulation VIP for PLB?

Simulation VIP for PLB is a Protocol Bridge IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.