Open Nand Flash Interface (ONFI) Synthesizable Transactor

Open Nand Flash Interface (ONFI) Synthesizable Transactor provides a smart way to verify the ONFI component of a SOC or a ASIC in…

Overview

Open Nand Flash Interface (ONFI) Synthesizable Transactor provides a smart way to verify the ONFI component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's ONFI Synthesizable Transactor is fully compliant with standard ONFI Specification 2.3/3.0/4.0/4.1/5.0 and provides the following features.

Key features

- Compliant with ONFI 2.3/3.0/4.0/4.1/5.0 specifications

- Supports source synchronous and asynchronous data interfaces

- Supports all mandatory and optional commands

- Supports 16 bit bus width operations

- Supports read ID commands

- Supports synchronous reset commands

- Interleaved commands support

- Multiple LUN operation support

- Multi-plane commands support

- Reset LUN command support

- Implicit DCC training commands support

- Read DQ training commands support

- Write TX DQ training pattern commands support

- Write TX DQ training readback commands support

- Write RX DQ training commands support

- Configurable timing modes for source synchronous and asynchronous data interface

- Supports partial page programming and copy back programming

- Source synchronous data interface supports clock stop feature

- Supports dual data bus

- Supports Data Bus Inversion(DBI)

- Supports small data move command for both program and copyback operations

- Ability to generate vendor specific commands and block abstracted NAND commands

- Rich set of configuration parameters to control ONFI functionality

- Supports constrained randomization of protocol attributes

- On-the-fly protocol and data checking

- Supports SDR, DDR, NV-DDR2, NV-DDR3, NV-LPDDR4 data interface

- Supports volume select commands

- Detects and reports the following errors:

- Page address error

- CRC error

- Command not support error

- Illegal command error

- Synchronous reset error

- Read ID error

- Reset LUN error

- Read cache error

- Read UID error

- Lun address change error

- Copyback program error

- Change row address error

- Read status enhanced error

- Interleave page address error

- Models, detects and notifies the test bench of significant events such as transactions, warnings, timing and protocol violations

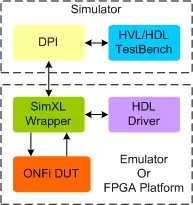

Block Diagram

Benefits

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

What’s Included?

- Synthesizable transactors

- Complete regression suite containing all the ONFI testcases

- Examples showing how to connect various components, and usage of Synthesizable Transactor

- Detailed documentation of all DPI, class, task and function's used in verification env

- Documentation contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Open Nand Flash Interface (ONFI) Synthesizable Transactor?

Open Nand Flash Interface (ONFI) Synthesizable Transactor is a Protocol Bridge IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.