Simulation VIP for OCP

In production since 2011 for dozens of designs.

Overview

In production since 2011 for dozens of designs.

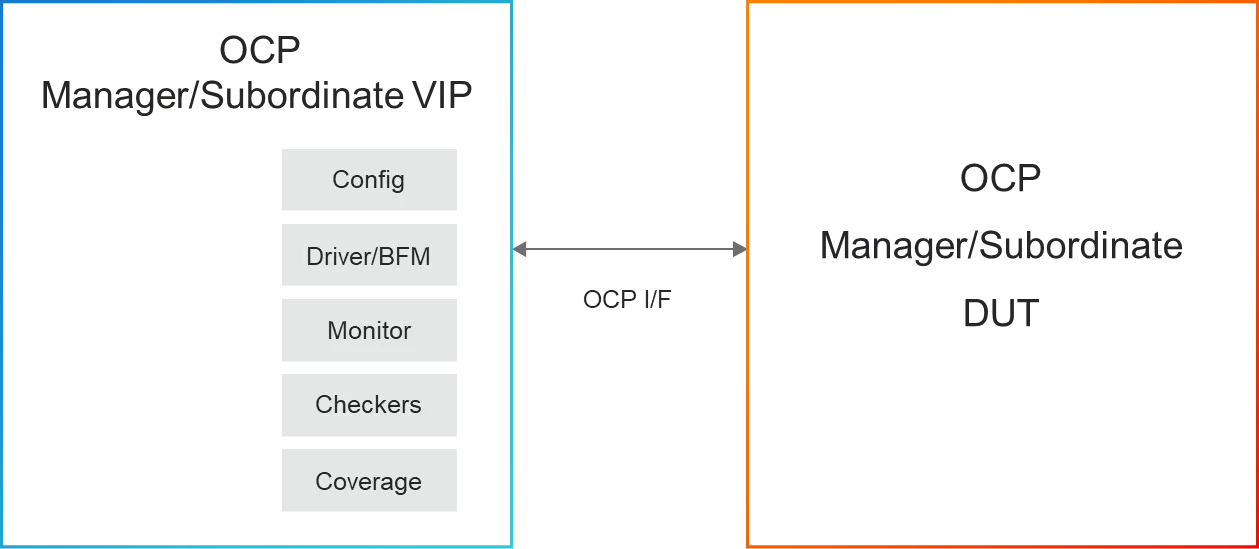

The Cadence OCP Verification IP (VIP) provides a mature, highly capable compliance verification solution for the OCP Protocol. Used on multiple production designs, the OCP VIP is applicable for Intellectual Property (IP), System-on-Chip (SoC), and system-level verification. The VIP is compatible with the industry standard Universal Verification Methodology (UVM) and runs on all leading simulators.

he Open Core Protocol International Partnership (OCP-IP) defines a point-to-point interface between two communicating entities, such as IP cores and bus interface modules (bus wrappers). One entity acts as the manager of the OCP instance and the other as the subordinate. Only the manager can present commands and is the controlling entity. The subordinate responds to commands presented to it.

Supported specification: OCP-IP Protocol v2.1, v2.2, and v3.0.

Key features

- Feature Name

- Description

- OCP Manager

- Full behavior of unlimited number of OCP managers capable of generating all types of OCP transfers

- Blocking and Non-Blocking Flow Control Options

- Supports both the blocking and non-blocking flow control options for the requests

- Cache Coherence Extension

- Partially supports the cache coherence feature. It supports both the main port and legacy port functionality. It supports only self-intervention as part of the intervention port functionality

- Clock Enable

- Supports the enable signal for clock

- Connect/Disconnect Feature

- Supports Connect-Disconnect feature for both Manager and Subordinate

- Enhanced Semantics for Write Response Enabled

- Ensures that the WRNP/WRC commands always have responses

- Multi-Threading and Tagging

- Supports multiple thread ids and multiple tag ids

- Out-Of-Order Response

- Supports out of order responses

- Request Interleaving

- Supports request interleaving. The interleaving depth is determined from the signal MAtomicLength

- Responding to Bus Traffic as an OCP Subordinate

- Emulates the full behavior of an unlimited number of OCP subordinates that respond to traffic over a bus and generates all types of responses to a DUT manager, according to OCP 2.2 Specification

- Synchronous and Asynchronous Reset

- Supports both synchronous and asynchronous reset. It also supports reset on the fly

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Simulation VIP for OCP?

Simulation VIP for OCP is a Protocol Bridge IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.