MIPI BIF Verification IP

The SmartDV's MIPI BIF Verification IP is fully compliant with Version 1.00 MIPI Alliance specification and verifies the Battery …

Overview

The SmartDV's MIPI BIF Verification IP is fully compliant with Version 1.00 MIPI Alliance specification and verifies the Battery Interface.It includes an extensive test suite covering most of the possible scenarios. It performs all possible protocol tests in a directed or a highly randomized fashion which adds the possibility to create the widest range of scenarios to verify the DUT effectively.

MIPI BIF Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

MIPI BIF Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports version 1.1 MIPI BIF Specification.

- Single wire,open drain communication interface

- Single Master and Multi-Slaves(up to 256 slaves)

- Supports Broadcast,Multicast and Unicast words.

- Supports various power modes.

- Supports all types of Bus commands.

- Supports UID procedure.

- Supports various kinds of errors generation and detection on BIF.

- General Communication Error

- Parity Error

- Inversion Error

- Invalid Word Length

- Timing Error

- Unknown Bus Command

- Wrong Command Sequence

- Bus Collision

- Slave Busy

- Slave Fatal Error

- Interrupt capability defined

- Supports the DDB Level 1 and Level 2 data structures.

- Supports various kinds of functions.

- Protocol function

- Slave control function

- NVM function

- Temperature sensor function

- Authentication function

- Glitch insertion and detection

- Monitor,Detects and notifies the testbench of all protocol and timing errors.

- Supports constraints Randomization.

- Status counters for various events in bus.

- Callbacks in master and slave for various events.

- MIPI BIF Verification IP comes with complete testsuite to test every feature of MIPI BIF specification.

- Functional coverage for complete MIPI BIF features.

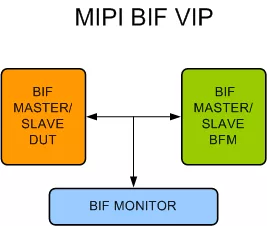

Block Diagram

Benefits

- Faster testbench development and more complete verification of MIPI BIF designs.

- Easy to use command interface simplifies testbench control and configuration of Master,Slave and Monitor.

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the MIPI BIF testcases.

- Examples showing how to connect various components and usage of Master, Slave and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI BIF Verification IP?

MIPI BIF Verification IP is a MIPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.