MIPI CSI-2 Verification IP

MIPI CSI-2 Verification IP Provides the mobile industry a standard, robust, scalable, low-power, high-speed, cost-effective inter…

Overview

MIPI CSI-2 Verification IP Provides the mobile industry a standard, robust, scalable, low-power, high-speed, cost-effective interface that supports a widerange of imaging solutions for mobile devices. MIPI CSI-2 Verification IP provides an smart way to verify the MIPI CSI-2 standard data transmission and control interfaces between transmitter and receiver. The SmartDV's MIPI CSI-2 Verification IP is fully compliant with version 4.0 MIPI Alliance specification for serial Interface and provides the following features.

MIPI CSI-2 Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

MIPI CSI-2 Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Full MIPI CSI2 Tx/Rx functionality

- Compliant with MIPI CSI2 Bus Specification v1.0 to v1.3, v2.0 to v2.10,v3.0,v4.0.

- Supports both DPHY and CPHY.

- Supports forward escape ULPM on all Data Lanes.

- Supports image applications with varying pixel formats from 6 to 24 bits per pixels.

- Supports all types of short packets.

- Supports all types of long packets.

- Supports all lane configurations.

- Supports all virtual channel identifier.

- Supports virtual channel extension field.

- Supports line and frame synchronization packets.

- Supports data scrambling.

- Supports skew calibration.

- Supports Smart Region of Interest (SROI).

- Supports Unified Serial Link (USL).

- Supports Always-On Sentinel Conduit (AOSC).

- Supports Latency Reduction and Transport Efficiency(LRTE)

- Supports Glitch insertion in multiple lanes.

- Supports various methods to interleave the transmission of different image data formats

- Interleaved data transmission using data type value

- Interleaved data transmission using virtual channels

- Supports various methods to interleave the data transmission using data type value

- Packet level interleaved data transmission

- Frame level interleaved data transmission

- Supports PHY-Protocol Interface (PPI).

- Supports high speed mode of operation.

- Supports various kinds of Tx and Rx errors generation and detection

- SoT error

- Sync error

- Word count error

- Sync length error

- Checksum error

- ECC error

- Monitor Detects and notifies the testbench of all protocol and timing errors.

- Supports constraints Randomization.

- Supports Compression for RAW Data Types.

- Status counters for various events in bus.

- Callbacks in node transmitter, receiver and monitor for user processing of data.

- MIPI CSI-2 Verification IP comes with complete test suite to test every feature of MIPI CSI-2 specification.

- Functional coverage for complete MIPI CSI-2 features.

- Control bus is supported by means of CSI.

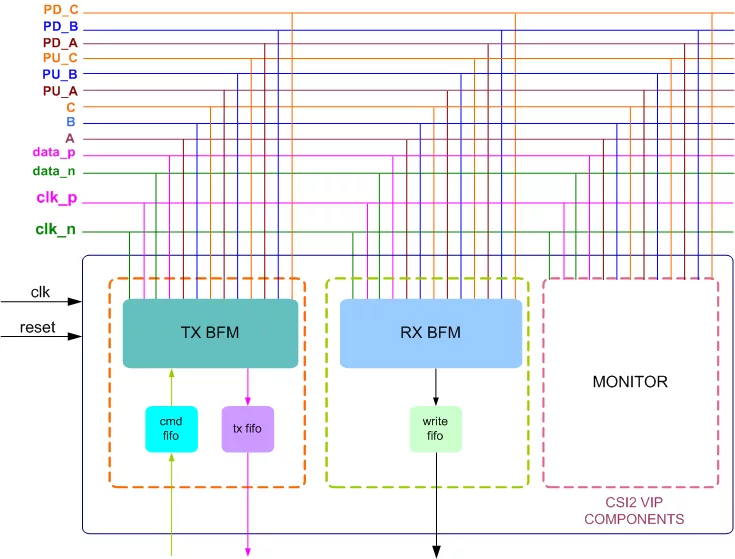

Block Diagram

Benefits

- Faster testbench development and more complete verification of MIPI CSI-2 designs.

- Easy to use command interface simplifies testbench control and configuration of Tx,Rx and monitor

- Simplifies results analysis.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the MIPI CSI-2 testcases.

- Examples showing how to connect various components, and usage of Tx,Rx and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI CSI-2 Verification IP?

MIPI CSI-2 Verification IP is a MIPI IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.