Simulation VIP for AMBA LPI

Cadence provides a mature and comprehensive Verification IP (VIP) for the LPI specification which is part of the Arm® AMBA® famil…

Overview

Cadence provides a mature and comprehensive Verification IP (VIP) for the LPI specification which is part of the Arm® AMBA® family of protocols. Incorporating the latest protocol updates, the Cadence® Verification IP for LPI provides a complete bus functional model (BFM), integrated automatic protocol checks, and coverage model. Cadence provides Interconnect Validator connection for interconnect verification that verifies the correctness and completeness of data as it passes through the SoC. Designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels, the VIP for LPI helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP runs on all major simulators and supports SystemVerilog and e verification languages along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported specification: Arm® Q-Channel and P-Channel Interfaces of Low Power Interface Specification

Key features

- Agent Type

- Power Controller or Device

- P-Channel

- Supports P-Channel functionality

- Q-Channel

- Supports Q-Channel functionality

- Delay Control

- Comprehensive control of timing aspects

- Reset Release

- Release of Q-Channel device from reset either with QREQn set to LOW or HIGH

- Controllability

- Both QACTIVE and PACTIVE can be independently controlled through register writes

- QACTIVE Bypass

- Bypassing of QACTIVE is possible when not required

- PACTIVE Width Configuration

- Configurable PACTIVE signal width

- Configurable Initial Values

- Initial QACTIVE and PACTIVE value can be configured to either HIGH or LOW

- Waveform Debugger

- All the channel states are visible through Waveform Debugger

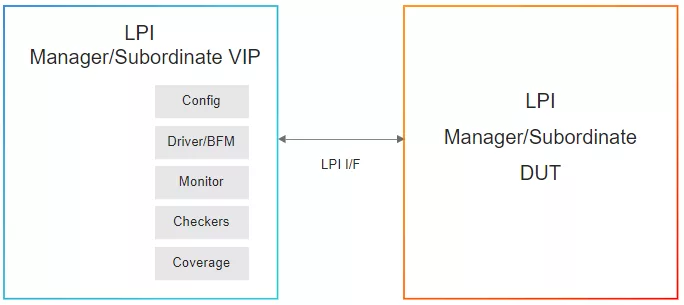

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Simulation VIP for AMBA LPI?

Simulation VIP for AMBA LPI is a Protocol Bridge IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.