RISC-V Display Connectivity Subsystem (DCS)

Overview

Modern display links have evolved into complex communication systems requiring continuous management of authentication, topology, link training, and runtime error recovery. Traditional implementations rely on host processors and operating systems to manage these functions, creating reliability and security dependencies between the display interface and the application processor.

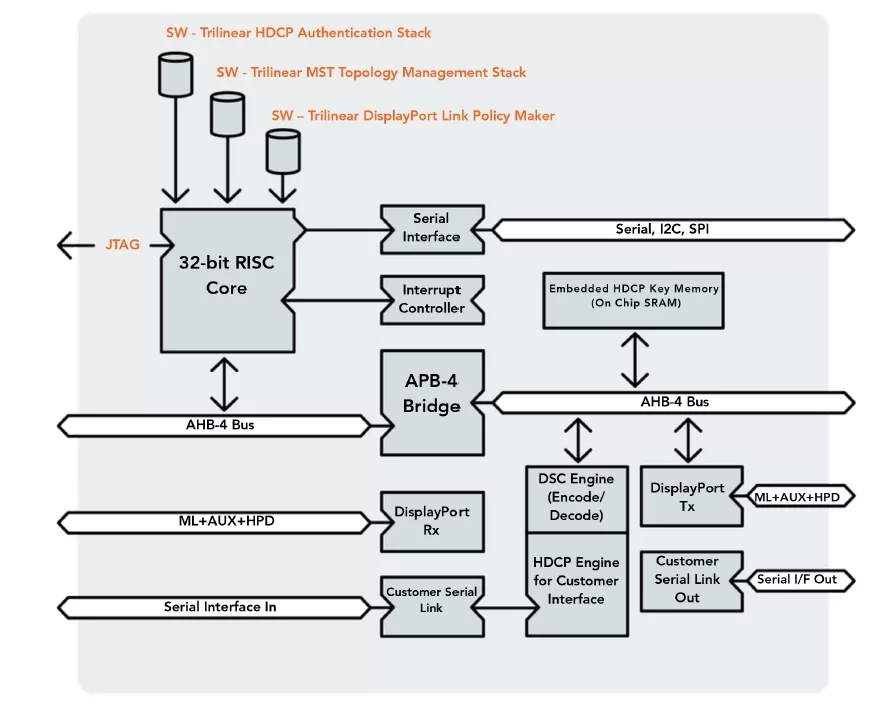

The Trilinear RISC-V Display Connectivity Subsystem (DCS) introduces a dedicated display control domain. A tightly integrated RISC-V processor supervises DisplayPort interfaces, content protection engines, and compression hardware, enabling autonomous operation independent of host software availability.

The subsystem separates the display control plane from the video data plane. The host configures display intent, while the DCS executes link behavior, policy management, and protocol compliance.

Key features

- Integrated 32-bit RISC-V control-plane processor supervising display connectivity

- Silicon proven across multiple ASIC and FPGA processes with third-party PHY partners

- Supports 1, 2, or 4 pixels per input cycle (up to 16K resolution per source)

- 1.62-20 Gbps link rates (DisplayPort 1.4a compliant at 8.1 Gbps)

- SST and MST operation with topology discovery and management

- Real-time HDCP 1.4 / HDCP 2.3 authentication

- Integrated Display Stream Compression with Forward Error Correction

- Optional eDP 1.5 including Panel Replay support

- Deep color and HDR support up to 16 bits of color

- External PHY interface (7 nm to 65 nm ASICs and FPGA targets)

- Autonomous link management independent of host processor

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Displayport IP core

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is RISC-V Display Connectivity Subsystem (DCS)?

RISC-V Display Connectivity Subsystem (DCS) is a Displayport IP core from Trilinear Technologies, Inc. listed on Semi IP Hub.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.