Rapid IO 4.0/3.1/2.2 PHY

RapidIO is a high performance, low pin count, packet switched, full duplex, system level interconnect architecture.

Overview

RapidIO is a high performance, low pin count, packet switched, full duplex, system level interconnect architecture. The architecture addresses the need for faster bus speeds in an intra-system interconnect for microprocessors, digital signal processors and communications. RapidIO interconnect architecture is partitioned into a layered hierarchy of specifications which includes Logical, Common Transport and Physical layers, in which the Physical layer defines the interface between two devices and the packet transport mechanism, flow control and electrical characteristics. The RapidIO PHY offers the physical layer specification solution as defined in the RapidIO Specification Rev 4.0/3.1/2.2. The IP supports four-lane running at different transmission speeds up to 6.25/ 10.3125/25.78125Gbps.

Key features

- 4 Channel per Quad

- Shared Quad common PLL architecture

- Digitally-control-impedance termination resistors

- Configurable TX output differential voltage swing

- Built-in TX De-Emphasis

- RX Built-in CTLE and Decision Feedback Equalization

- Wide Range Phase-Interpolator Based Digital CDR

- PLL Frequency Lock detection

- Analog DC Testing

- Support RX Built-in Eye Opening Monitor

- Support Boundary Scan Interface for Serial link, compliant with IEEE 1149.6-2003/ 1149.1-2001

- BIST (PRBS-7, PRBS-15, PRBS-23, PRBS-31) generator and checker

- Support Loopback for the Far-end and Near-end testing

- Integrated Power-on and reset logic

- JTAG/APB control registers access

- Low Power Consumption

- Supports Flip-Chip package

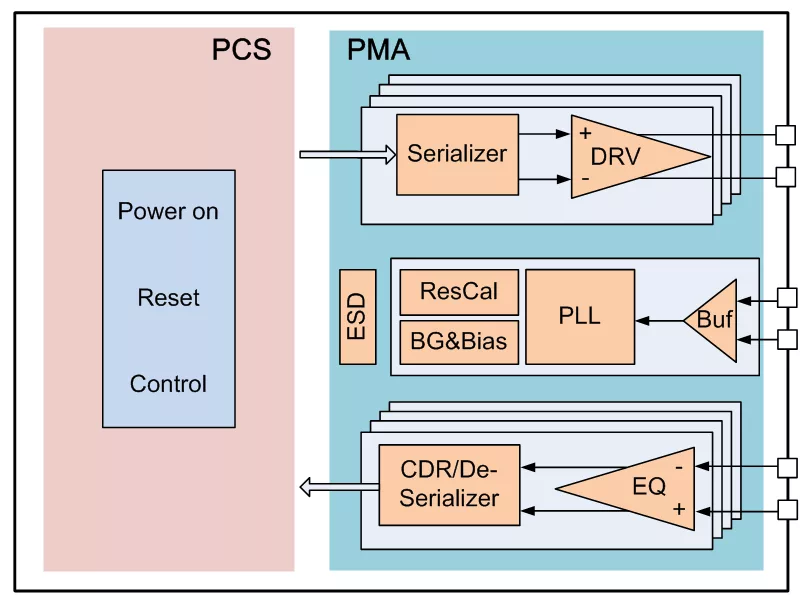

Block Diagram

What’s Included?

- GDSII&CDL Netlist

- Verilog Model

- LEF Layout Abstract(.LEF)

- Liberty Timing Models(.lib)

- Verify Results

- Specification

- Datasheet

- Integration Guideline

- Evaluation Plan

- Leading support for package design, SI&PI modeling and production test development

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about RapidIO IP core

How to pick a RapidIO switch

Tips for maximizing RapidIO

RapidIO moves up to Fabric

Enter the Inner Sanctum of RapidIO: Part 1

Enter the Inner Sanctum of RapidIO: Part 2

Frequently asked questions about RapidIO IP cores

What is Rapid IO 4.0/3.1/2.2 PHY?

Rapid IO 4.0/3.1/2.2 PHY is a RapidIO IP core from KNiulink Semiconductor Ltd. listed on Semi IP Hub.

How should engineers evaluate this RapidIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this RapidIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.