RapidIO Verification IP

RapidIO Verification IP provides an smart way to verify the RapidIO bi-directional two-wire bus.

Overview

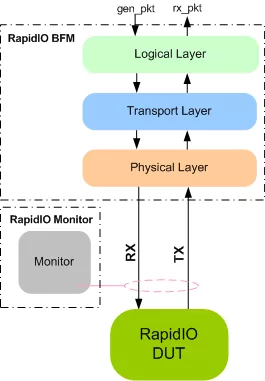

RapidIO Verification IP provides an smart way to verify the RapidIO bi-directional two-wire bus. The SmartDV's RapidIO Verification IP is compliant with RapidIO Trade Association, RapidIO Interconnect Specification version 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1. RapidIO VIP is implemented in a layered fashion. which is basically divided into a physical layer, transport layer and logical layer. The SmartDV's RapidIO Verification IP has both the incarnations of RapidIO technology :Parallel RapidIO and Serial RapidIO(SRIO).

The RapidIO VIP monitor acts as powerful protocol-checker, fully compliant with RapidIO specification. The RapidIO VIP includes an extensive test suite covering most of the possible scenarios. It performs all possible protocol tests in a directed or a highly randomized fashion which adds the possibility to create the widest range of scenarios to verify the DUT effectively.

RapidIO Verification IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

RapidIO Verification IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports RapidIO specification 1.3, 2.0, 2.1, 2.2, 3.0, 3.1, 3.2, 4.0 and 4.1.

- Supports Serial 1x/2x/4x/8x and 16x Physical lanes.

- Supports 8b/10b and 64b/67b Encode and Decode functions.

- Supports scrambler/Descrambler.

- Supports 1.25 Gbaud, 2.5 Gbaud, 3.125 Gbaud, 5 Gbaud, 6.25 Gbaud, 10.3125 Gbaud, 12.5 Gbaud and 25.78125 Gbaud lane rate.

- Supports 66, 50 and 34-bit addressing on the RapidIO interface.

- Supports Parallel Physical 8/16 bits interfaces.

- Supports all types of packets and sizes.

- Supports all types of IDLE sequences, Control and Status Symbols.

- Supports 8-bit, 16-bit and 32-bit device IDs.

- Automatic freeing of resources used by acknowledged packets.

- Supports I/O system, message passing and globally shared distributed memory (GSM).

- Supports communication with mailboxes via messages.

- Supports generation and reaction to flow control.

- Supports out of order transaction delivery based on the prioritization.

- Supports critical request flow ordering.

- Very flexible to insert errors in serial lanes.

- Supports Error Management Extensions.

- Provides error injection and error detection with a wide variety of error types, Which includes

- Under and oversize packet.

- CRC errors.

- Invalid code group insertion.

- Invalid /K/ characters insertion.

- Lane Skew insertion.

- Error on control symbol.

- Unsupported packet types.

- Supports cancellation and retrying of packets mechanisms.

- Support all types of timing and protocol violation detection.

- Supports constraints Randomization.

- Status counters to keep track of various events, Which includes

- Corrupted/uncorrupted packets.

- Corrupted/uncorrupted control symbols.

- Type of packet.

- CRC error.

- Total number of errors detected.

- Supports callbacks for user to get packets or errors in HOST/DEVICE and monitor.

- RapidIO verification IP comes with complete testsuite to test every feature of RapidIO spec and also as per RIO LAB testsuite.

- Functional coverage for each functional condition in env.

- Notifies the testbench of significant events such as transactions, warnings, timing and Protocol violations.

Block Diagram

Benefits

- Rich set of configuration parameters to control the functionality.

- Faster test bench development and more complete verification of RAPIDIO designs.

- Simplifies results analysis.

- Integrates easily into OpenVera, SytemVerilog, SystemC, Verilog.

- Runs in every major simulation environment.

What’s Included?

- Complete testsuite to test every feature of RapidIO spec and also as per RIO LAB testsuite.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about RapidIO IP core

How to pick a RapidIO switch

Tips for maximizing RapidIO

RapidIO moves up to Fabric

Enter the Inner Sanctum of RapidIO: Part 1

Enter the Inner Sanctum of RapidIO: Part 2

Frequently asked questions about RapidIO IP cores

What is RapidIO Verification IP?

RapidIO Verification IP is a RapidIO IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this RapidIO?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this RapidIO IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.