Vendor:

T2M GmbH

Category:

SPI / QSPI XSPI

QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)

The SPI is a fully configurable SINGLE, DUAL, QUAD and OCTAL SPI master/slave device, which allows user to configure polarity and…

Overview

The SPI is a fully configurable SINGLE, DUAL, QUAD and OCTAL SPI master/slave device, which allows user to configure polarity and phase of serial clock signal SCK. The SPI controller is fully compatible with the Hyper BusTM specification, xSPI (Expanded Serial Peripheral Interface – JESD251A) specification and XccelaTM Bus Interface. The SPI Controller allows easy communication with most available SPI FLASH memories. A serial clock line (SCK) synchronizes shifting and sampling of the information on the serial data lines. It is a technology independent design that can be implemented in a variety of process technologies. The SPI system is flexible enough to interface directly with numerous standard product peripherals from several manufacturers. Clock control logic allows a selection of clock polarity and a choice of two fundamentally different clocking protocols to accommodate most available synchronous serial peripheral devices. The SPI can automatically drive selected by SSCR (Slave Select Control Register) slave select outputs (SS3O – SS0O), and address SPI slave device to exchange serially shifted data. It supports two DMA modes: single transfer and multi-transfer. These modes allow SPI to interface to higher performance DMA units, which can interleave their transfers between CPU cycles or execute multiple byte transfers. SPI is fully customizable, which means it is delivered in the exact configuration that meets users’ requirements.

Key features

- Set of software accessible control registers to execute any Flash memory command

- Supports any device clock frequency, polarity and phase,

- Programmable baud rate generator,

- Built in FLASH Commands decoder supports most popular FLASH devices,

- Optional built in AES Encoder/Decoder

- DMA support

- Support for various SPI Bus Standards: Hyper BusTM, xSPI, XccelaTM

- Compliant with AMBA2 Specification, supports APB, AHB, AXI bus interfaces

- Single, Dual, Quad and OCTAL SPI transfer/reception

- Execute in place – XIP functionality support

- Data Bus Size configuration to 8, 16 or 32 bits wide

- Optional FIFO size extension

- Maximum supported Flash address range – 32 bits

- Up to 4 SPI slaves can be addressed

- Software Slave Select Output – SSO – selection

- Automatic Slave Select outputs assertion

- System error detection

- Interrupt generation

- Bit rates generated as 1/ 2.. 1/255 of system clock.

- Four SPI transfer formats supported: CPOL/CPHA.

- Simple interface allows easy connection to microcontrollers

- Fully synthesizable, static synchronous design with no internal tri-states

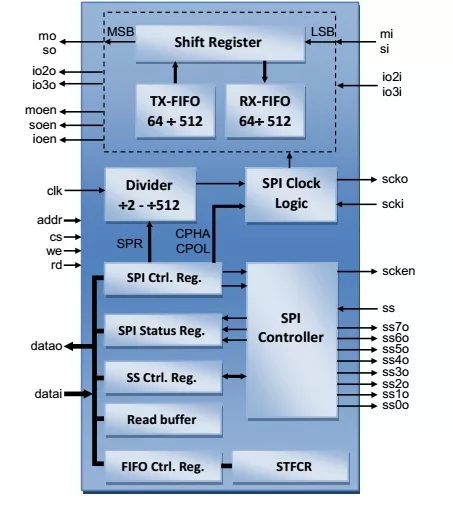

Block Diagram

Quad SPI Flash Controller IP block diagram

Applications

- Embedded microprocessor boards

- Consumer and professional audio/video

- Home and automotive radio

- Low-power applications

- Communication systems

- Digital multimeters

What’s Included?

- Source code:

- VHDL Source Code or/and

- VERILOG Source Code or/and

- Encrypted, or plain text EDIF

- VHDL & VERILOG test bench environment

- Active-HDL automatic simulation macros

- Model Sim automatic simulation macros

- Tests with reference responses

- Technical documentation

- Installation notes

- HDL core specification

- Datasheet

- Synthesis scripts

- Example application

- Technical support

- IP Core implementation support

- 3 months maintenance

- Delivery of the IP Core and documentation updates, minor and

- major versions changes

- Phone & email support

Specifications

Identity

Part Number

Quad SPI Flash Controller IP

Vendor

T2M GmbH

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

T2M GmbH

T2M GmbH is the leading Global Technology Company supplying state of the art complex semiconductor connectivity IPs and KGDs, enabling the creation of complex connected devices for Mobile, IoT and Wearable markets.

T2M's unique SoC White Box IPs are the design database of mass production RF connectivity chips supporting standards including Wifi, BT, BLE, Zigbee, NFC, LTE, GSM, GNS. They are available in source code as well as KGD for SIP / modules.

With offices in USA, Europe, China, Taiwan, South Korea, Japan, Singapore and India, T2M’s highly experienced team provides local support, accelerating product development and Time 2 Market.

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support)?

QSPI FLASH Controller – XIP functionality (SINGLE, DUAL and QUAD SPI Bus Controller with Double Data Rate support) is a SPI / QSPI XSPI IP core from T2M GmbH listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.