SPI Master Serial Interface Controller

The SPI_MASTER IP Core is an SPI compliant serial interface controller capable of driving up to 16 different slave devices in ful…

Overview

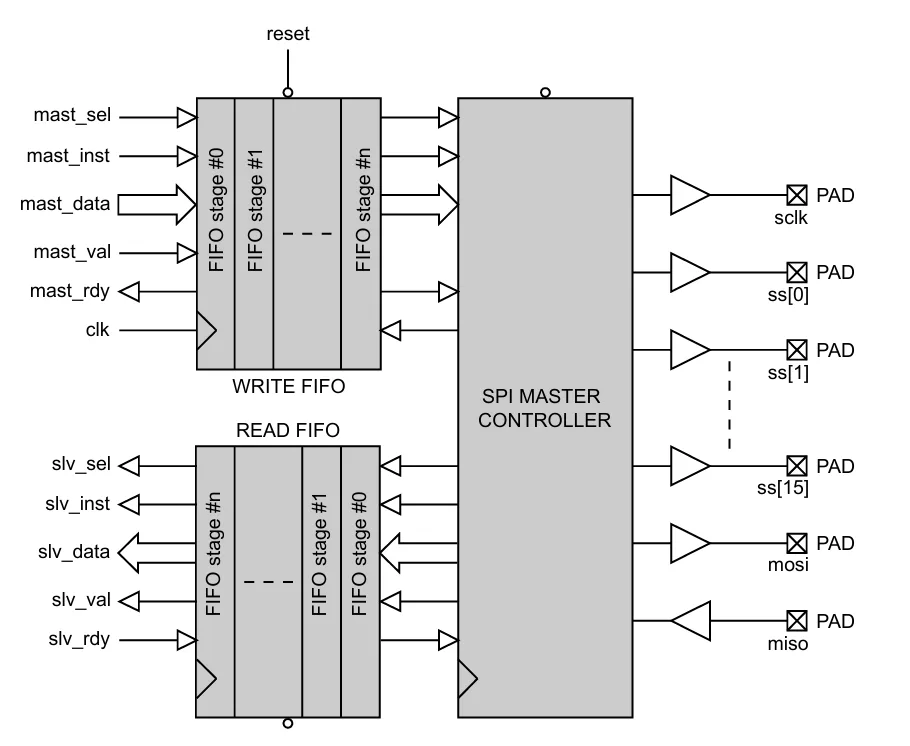

The SPI_MASTER IP Core is an SPI compliant serial interface controller capable of driving up to 16 different slave devices in full-duplex operation. The controller receives data and instructions via the master instruction interface. These instructions are then processed by the controller core in order to generate the appropriate signals on the SPI bus. The serial slave data on the SPI bus is also captured by the controller and de-serialized for presentation at the slave read data port.

The SPI master controller is comprised of three main blocks. These blocks are the master instruction write FIFO, the SPI controller core and the slave read-data output FIFO.

The serial clock-period is determined by the generic parameter t_period. This parameter specifies the sclk period in system clock cycles. As an example, if the system clock 'clk' is running at 130 MHz and a serial clock frequency of 10 MHz is required, a value of t_period = 13 should be specified. In addition, the generic parameters cpol and cpha permit the clock polarity and phase characteristics to be specified as per the SPI specification. The table below shows a brief summary of these settings.

Key features

- Synthesizable, technology independent IP Core for FPGA, ASIC and SoC

- Supplied as human readable VHDL (or Verilog) source code

- SPI serial-bus compliant

- Supports up to 16 slave devices

- Intuitive command interface featuring a simple valid-ready handshake protocol

- Input/output FIFOs permit queuing of sequential SPI requests and corresponding read data

- Architecture allows sustained 8-bit read/write operations

- Configurable serial clock frequency

- Configurable clock polarity setting (CPOL)

- Configurable clock phase setting (CPHA)

- Capable of full-duplex or half-duplex operation

- Data rates of up to 40 Mbps+

Block Diagram

Applications

- Driving SPI slave devices

- Inter-chip board-level communications

- Robust communication at higher data rates than other serial protocols such as I2C, UART and USB 1.0

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is SPI Master Serial Interface Controller?

SPI Master Serial Interface Controller is a SPI / QSPI XSPI IP core from Zipcores Electronic Systems Engineering S.L. listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.