SPI Master DO-254 IP Core

The SPI Master IP Core implements an SPI Master fully compliant to the SPI Standard (Motorola’s M68H11 Reference Manual).

Overview

The SPI Master IP Core implements an SPI Master fully compliant to the SPI Standard (Motorola’s M68H11 Reference Manual).

The Serial Peripheral Interface (SPI) bus is a synchronous serial communication interface specification used for short distance communication, primarily in embedded systems. The interface was developed by Motorola and has become a de facto standard. Typical applications include Secure Digital cards and liquid crystal displays. SPI devices communicate in full duplex mode using a master-slave architecture with a single master. The master device originates the frame for reading and writing. Multiple slave devices are supported through selection with individual slave select (SS) lines.

The SPI Master IP Core has been developed to DAL A according to the DO-254 / ED-80 and is accompanied by a Certification Kit. For lower DAL levels reduced documentation sets are available. The core is also available as a netlist for DAL D or projects not needing the full RTL source.

Safe Core Devices provides two separate IP Cores, one for the SPI Master IP Core and one for the SPI Slave IP Core. If the system needs to be capable of transmitting and receiving both cores can be instantiated in the target device.

Implementation Details

Unless otherwise specified all the runs have been performed with the default options of the respective tool. Register placement on the IO has been disabled.

No constraints were added, so the results listed under the column “Maximum frequency of operation” are the worst case scenario (no multicycle, false paths, etc. defined).

The results are provided for an 8-bit word SPI Master Core, g_NUM_OF_SLAVES = 1, g_SCK_DIVIDER = 15 and without TMR (Triple Module Redundancy), if TMR is used the number of registers will be triplicated, the combinatorial logic will also increase and there might be a penalty on the maximum ‘clk‘ frequency.

ACTEL / MICROSEMI

| FPGA Type | Maximum ‘clk‘ Frequency | Logic Modules (CORE) |

|---|---|---|

| ProASIC3

(A3P015 68QFN I Std) |

110 MHz | 106 |

| IGLOO

(AGL030V5 100VQPF I Std) |

116 MHz | 103 |

| Fusion

(AFS090 180QFN I Std) |

110 MHz | 106 |

| Axcelerator

(RTAX250S 208CQFP Mil Std) |

144 MHz | SEQUENTIAL (R-cells): 36

COMB (C-cells): 39 |

ALTERA

| FPGA Type | Maximum ‘clk’ Frequency | Flip-Flops | ALUTs | ALMs | Logic Cells |

|---|---|---|---|---|---|

| MAX II

(EPM240F100I5) |

150 MHz | 34 | – | – | 53 |

| Cyclone III

(EP3C5E144I7) |

317 MHz | 34 | – | – | 58 |

| Stratix II

(EP2S60F484I4) |

336 MHz | 34 | 33 | 25 | – |

| Stratix III

(EP3SE110F780I3) |

> 550 MHz | 34 | 33 | 24 | – |

| Stratix IV

(EP4SGX70HF35C2) |

> 650 MHz | 34 | 33 | 25 | – |

XILINX

| FPGA Type | Maximum ‘clk‘ Frequency | Flip-Flops | 4-LUTs | Slices | Macrocells |

|---|---|---|---|---|---|

| CoolRunnerII

(XC2C128-6-TQ144) |

87 MHz | 33 | – | – | 36 |

| Spartan3

(XC3S50-5PQ208) |

187 MHz | 30 | 80 | 50 | – |

| Virtex2

(XC2V40-4FG256) |

206 MHz | 30 | 80 | 50 | – |

| Virtex4

(XC4VLX15-12SF363) |

> 390 MHz | 32 | 80 | 51 | – |

| Virtex5

(XC5VLX30-3FF324) |

> 550 MHz | 33 | – | 17 | – |

Key features

- Design Assurance Level A according to RTCA DO-254/ED-80 (April, 2000)

- Fully compliant to the SPI Standard (Motorola’s M68H11 Reference Manual)

- Configurable data rate

- Configurable phase, polarity and word size

- Configurable number of slaves

- Single clock domain fully synchronous design

- Simple interface to user’s logic

- TMR coded for SEU immunity (optional)

- Technology independent (can be synthesized to any FPGA/CPLD vendor)

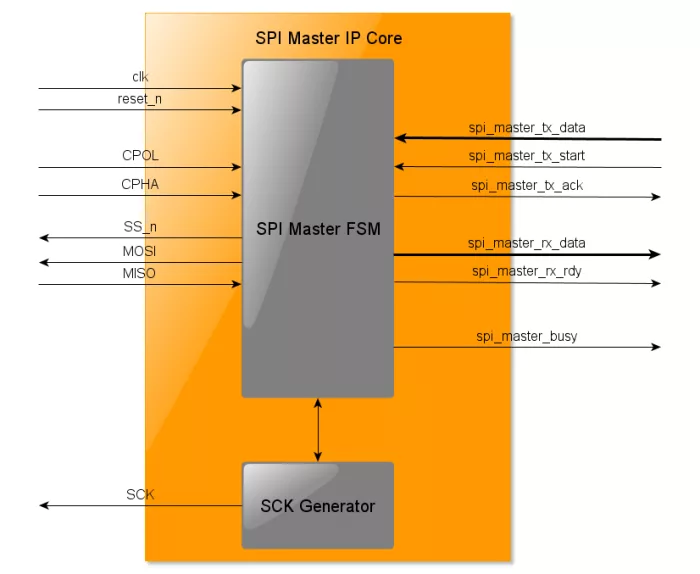

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is SPI Master DO-254 IP Core?

SPI Master DO-254 IP Core is a SPI / QSPI XSPI IP core from SafeCore Devices listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.