Vendor:

eSi-RISC

Category:

SPI / QSPI XSPI

APB SPI (Serial Peripheral Interface) master and slave

The eSi-SPI core is a Serial Peripheral Interface that can be used to implement full-duplex, synchronous, serial communications b…

Overview

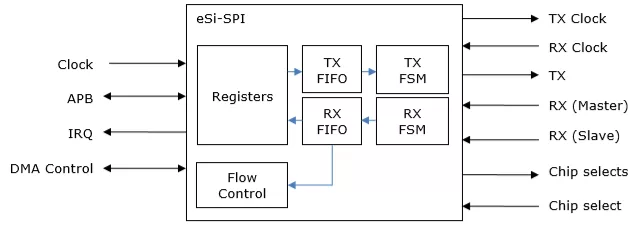

The eSi-SPI core is a Serial Peripheral Interface that can be used to implement full-duplex, synchronous, serial communications between ICs. The eSi-SPI core can operate as a SPI master or slave. Multiple chip-selects are supported in master mode, to allow connection to multiple slave devices. The SPI is supplied with an AMBA APB slave interface and so can be driven by software or via DMA.

Key features

- Master or slave operation.

- Programmable word size (1 to 32 bits).

- Programmable bit ordering (MSB first / LSB first).

- Programmable clock polarity (CPOL) and phase (CHPA).

- Programmable bit rate.

- Automatic and manual chip-select generation.

- Multiple chip-select outputs.

- Configurable TX and RX FIFO.

- Configurable support for parallel as well as serial transfers.

- Supports multi-master and multi-slave operation.

- Auto TX and RX to reduce bus bandwidth requirements.

- AMBA 3 APB slave interface.

- DMA flow-control interface.

Block Diagram

eSi-SPI block diagram

What’s Included?

- Verilog RTL

- Testbench

- Simulation and synthesis scripts

- Documentation

- C API

Specifications

Identity

Part Number

eSi-SPI

Vendor

eSi-RISC

Type

Silicon IP

Files

Note: some files may require an NDA depending on provider policy.

Provider

eSi-RISC

HQ:

UK

eSi-RISC designs and licenses the eSi-RISC range of configurable, low-power, RISC CPU IP cores, as well as associated peripheral IP cores and software development tools. The eSi-RISC processors are unique in being configurable from a base 16-bit core (eSi-1600) to a 32-bit, multi-core CPU with optional caches (eSi-3250), to a high-performance DSP core with 64-bit fixed-point SIMD and floating point support (eSi-3264).

As well as supplying individual cores, eSi-RISC can develop complete SoC sub-systems combining CPUs, memory and peripherals (DMA, memory-controllers, I2C, UART, SPI, etc.), using an AMBA AXI/AHB/APB based interconnect, generated automatically using our eSi-SoC EDA tool.

Learn more about SPI / QSPI XSPI IP core

Unleashing the Power of Communication: Exploring the XSPI Protocol and Arasan Chip Systems' XSPI IP Portfolio

Frequently asked questions about SPI / QSPI / xSPI IP cores

What is APB SPI (Serial Peripheral Interface) master and slave?

APB SPI (Serial Peripheral Interface) master and slave is a SPI / QSPI XSPI IP core from eSi-RISC listed on Semi IP Hub.

How should engineers evaluate this SPI / QSPI XSPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this SPI / QSPI XSPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.