ASA Motion Link PHY

Overview

The Mixel Automotive SerDes Alliance Motion Link (ASA-ML) PHY is a high-speed Automotive SerDes solution compliant with the Automotive SerDes Alliance (ASA) Motion Link standard. Mixel was the first IP provider to announce support for this IP in 2025.

It provides an asymmetric high-bandwidth link optimized for automotive applications, enabling efficient connectivity between cameras, sensors, and displays in modern vehicle architectures.

It supports multi-gigabit data rates, up to 8 Gbps downstream and up to 4 Gbps upstream, depending on the target application and use case.

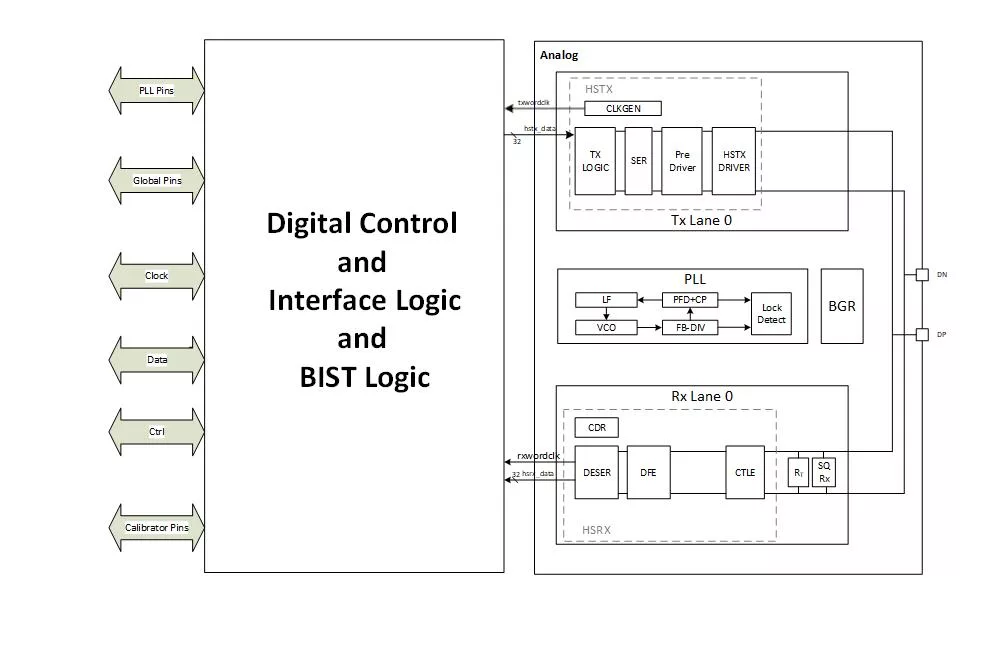

The PHY is organized at the lane level, where each lane comprises analog and digital components. The digital portion manages lane operation by controlling the analog front-end and interfacing with the Data Link layer, ensuring proper coordination between data processing and high-speed signaling.

On the transmit (TX) side, the analog front-end includes a serializer and transmitter. The serializer converts parallel data into a serial bitstream, which is then driven onto the channel by the transmitter. On the receive (RX) side, the incoming serial data is recovered and converted back into parallel data using a clock-and-data recovery mechanism and a deserializer, ensuring accurate data reconstruction.

The PHY is designed to operate over typical automotive channels, including coaxial cables and shielded twisted pair (STP), supporting reach on the order of several meters up to 10–15 meters, depending on cable quality, data rate, and system design. Advanced equalization techniques in the receiver compensate for channel loss and signal degradation, enabling robust performance over challenging automotive channel conditions.

This lane-based architecture, combining digital control with high-performance analog transmission and reception, enables robust, high-speed, and scalable data communication across automotive links.

Key features

- Supports Automotive SerDes Alliance Transceiver Specification v2.1

- Supports up to 8 Gbps (Speed Grade 3) downstream for TX and RX directions

- Supports up to 4 Gbps (Speed Grade 2) upstream for TX and RX directions

- Supports different Equalization options for link speed enhancement

- RX Equalization (CTLE & DFE)

- TX FIR Equalization

- Analog Test Coverage through internal loopback

- Eye monitor for internal eye-opening measurement

- Supports differential signaling on STP cabling and single-ended signaling on coaxial cabling

- On-chip calibrator for resistance termination

- Line fault detection

- Automotive Grade ESD (4kV HBM and 750V CDM)

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is ASA Motion Link PHY?

ASA Motion Link PHY is a Single-Protocol PHY IP core from Mixel, Inc. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.