NoC System IP

The Janus Network on Chip (NoC) is a new configurable soft IP designed to speed up the system-on-chip (SoC) and full system desig…

Overview

The Janus Network on Chip (NoC) is a new highly configurable soft IP designed to speed up the system-on-chip (SoC) and full system design cycle by reducing some of the problems associated with large SoCs.

With many more processing nodes, as well as memory and I/O nodes designed into the SoC, the interconnect becomes a major design hurdle. Wiring congestion and wire loads introduce challenges to physical designs, specifically when routing large numbers of wires and meeting clock speed targets.

The Janus NoC addresses those challenges by employing multiple strategies:

- Packetization allows a reduction of the wire count

- Significant reduction of the complexity of large crossbars by partitioning them into smaller ones

- Introduction of pipelining to links with heavy loads, allowing the NoC to operate faster

Key features

- Reduces wire count and congestion

- Reduces physical design issues

- Handles gear change automatically

- Configurable to meet your PPA goals

- Easy to configure with a quick turnaround of configuration changes

- Use with Cadence simulation/emulation to identify bottlenecks and remove them

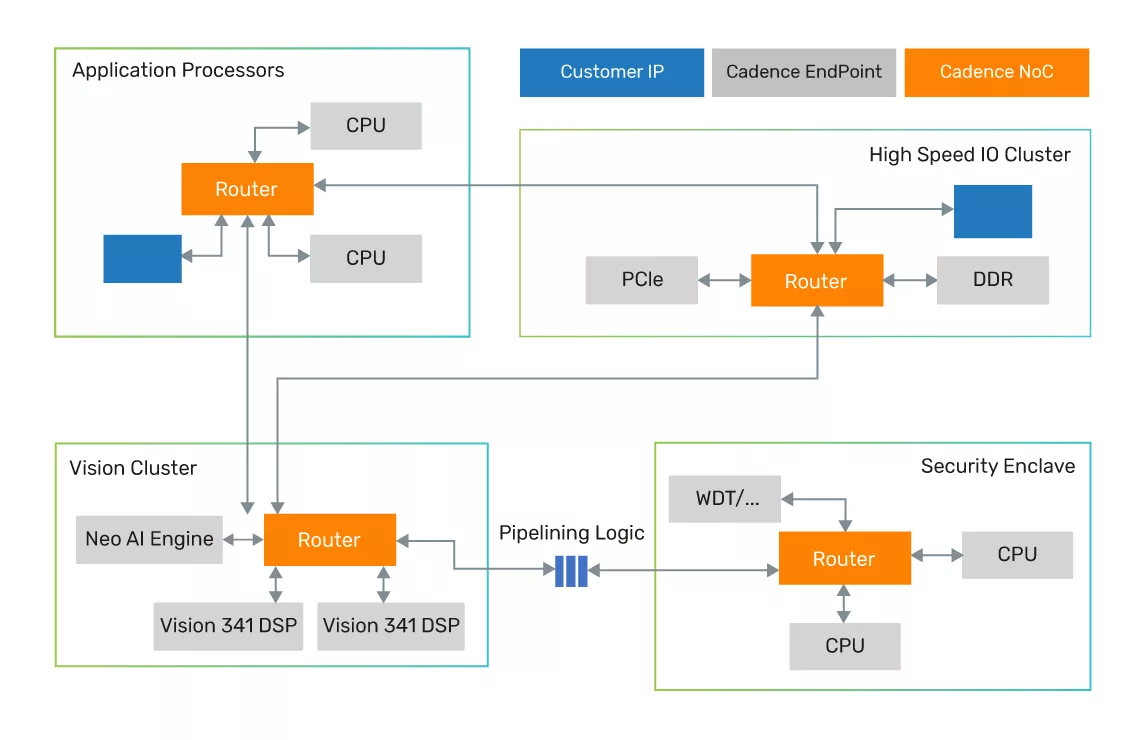

Block Diagram

Benefits

- Intuitive Design Entry Tool

- Use a powerful GUI to generate a NoC configuration, then submit the configuration to get RTL and SystemC models

- Highly Configurable

- Configure BW, latency, clock domain crossings, clock gating, buffer size, and pipeline stages—everything you need to achieve your target PPA goals

- Scalability

- Start with subsystem design, then take the same design and create a full SoC; Need a higher level of integration? No problem, we can do chiplets as well

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is NoC System IP?

NoC System IP is a Network-On-Chip IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.