AXI Interconnect

The AXI MATRIX-IP component is a multi-layer interconnect implementation of the AXI protocol, which is designed for high-performa…

Overview

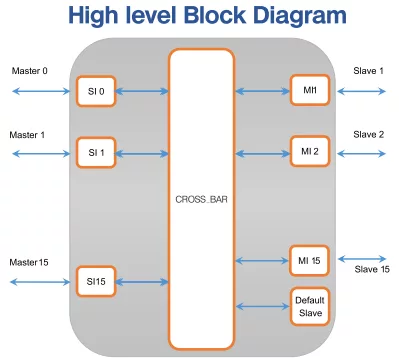

The AXI MATRIX-IP component is a multi-layer interconnect implementation of the AXI protocol, which is designed for high-performance, high-frequency system designs. AXI MATRIX-IP is highly configurable with the capacity to handle up to 16 Masters and Slaves. IP can be configured to support AXI3, AXI4-Lite or AXI4.

Mobiveil Inc. a proven Silicon IP provider for SSD Storage domain and High speed IO connectivity is offering proven AXI Interconnect IP solution for use in SOC applications. With this IP addition, Mobiveil offers complete set of IPs needed for accelerated SOC development that includes PCIe, DDR/LPDDR, Toggle/NAND, RISC-V Core, Interrupt Controller, QSPI, I2C, UART, GPIO, AXI-APB Bridge and Timer.

Key features

- Configurable Number of AXI Master (Slave interface SI) (1-16) (S0..S15)

- Configurable Number of AXI Slave (Master Interface MI) (1-16) (M0...M15)

- AXI Address Width ( 32 or 64)

- AXI Data width (32, 64, 128, 256, 512)

- AXI Slave ID width (MAS_ID_WIDTH + log2(AXI_Master ID_WIDTH)

- AXI BURST WIDTH (16 beats for AXI 3 and 256 beats for AX14)

- Configurable UP Sizer/Down Sizer for Master (SI)

- Configurable UP Sizer/Down Sizer for Slave (MI)

- Configurable Read acceptance Capability for the Master(SI)

- Configurable Write acceptance Capability for the Master(SI)

- Configurable Read issuing Capability for the Slave (MI)

- Configurable Write issuing Capability for the Slave(MI)

- Round Robin Arbitration scheme at Ml interface (to Slave Port)

- Round Robin Arbitration scheme at the SI interface (to Master port read /write response)

- Asynchronous Clock support for Master Interface (SI) and Slave Interface (MI)

- Out of order support for write response limited to 4 bit ID width (max 16 lds)

- Out of order support for read response/data limited to 4 bit ID width (max 16 IDs)

- Multiple REGION support for SOC slaves

- Trust-Zone Security feature support for Connected Slaves

- It only permits, if the slave is configured as secured slave

- Any Non secure transactions to the secure devices are blocked and it turns with DECERR response to the connected master

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is AXI Interconnect?

AXI Interconnect is a Network-On-Chip IP core from Mobiveil Inc. listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.