FlexNoC 5 Interconnect IP

Physically Aware Network-on-Chip IP The latest generation FlexNoC 5 Interconnect with its integrated physical awareness technolog…

Overview

Physically Aware Network-on-Chip IP

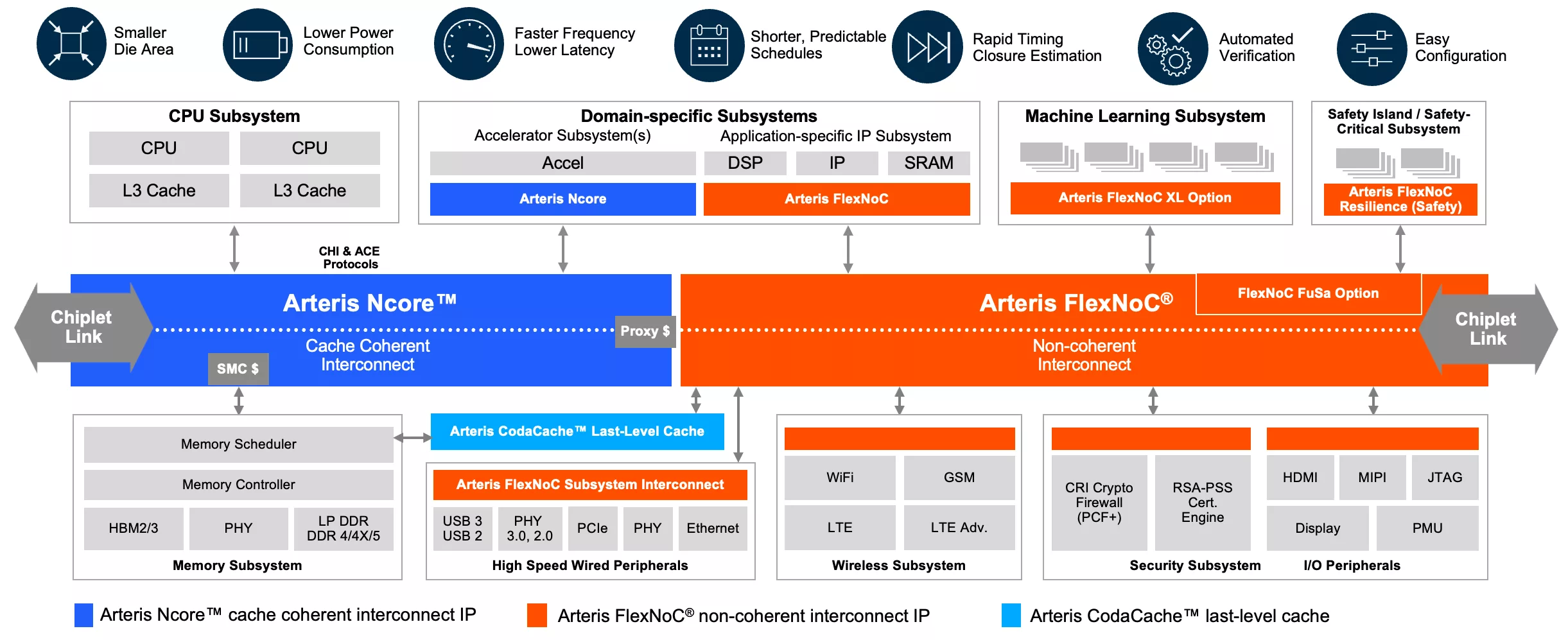

The latest generation FlexNoC 5 Interconnect with its integrated physical awareness technology, gives place and route teams a much better starting point while simultaneously reducing interconnect area and power consumption. FlexNoC 5 delivers up to 5X shorter turn-around-time versus manual physical iterations.

The combined use of FlexNoC and Ncore IP in an ASIC design delivers unparalleled performance optimization, scalability, and system integration, enabling robust cache coherence, efficient communication, and flexibility, leading to market differentiation and accelerated time-to-market.

Key features

- Auto-timing closure assist

- NIU (Network Interface Unit) tiling to organize NIUs into modular, repeatable blocks, improving scalability, efficiency, and reliability

- Topology visualized directly on floorplan

- Multi-clock/power/voltage domains and power management with unit-level clock gating

- Multi-protocol support including AMBA 5 with QoS bandwidth regulator and limiter Enumerations

- General optimizations for lower area e.g. up to 30% for some NoC elements depending on configuration

- Native and user-defined firewall security

- Import and export to Magillem tools

- AMBA 5 support of DVM 8.1 (Distributed Virtual Memory)

- On-chip performance monitoring and debug

- Debug and trace with ATB 128b and timestamps

Block Diagram

Benefits

- Flexible Topologies

- FlexNoC is generated from simple elementary components which are combined by a powerful set of underlying algorithms and an intuitive GUI, making it possible to build any topology.

- Small to Large SoCs

- FlexNoC easily supports long cross-chip paths by leveraging source-synchronous communications and virtual channels.

- Huge Bandwidth

- FlexNoC drives performant on-chip data flow and access to off-chip memory by enabling multi-channel HBMx memory and high bandwidth data paths.

Applications

- Automotive,

- Mobility,

- Wireless,

- Consumer Electronics,

- IoT,

- Server,

- Networking and Industrial SoCs

What’s Included?

- FlexNoC 5 Physically Aware Interconnect IP

- Configuration tools

- Automated testbench generator

- Documentation, training, and support.

- Safety Manual -- when licensed with the Functional Safety (FuSa) Option

Video

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Network-On-Chip IP core

How Network-on-Chip Architectures Are Powering the Future of Microcontroller Design

Why verification matters in network-on-chip (NoC) design

SoC design: When a network-on-chip meets cache coherency

Accelerating RISC-V development with network-on-chip IP

Network-on-chip (NoC) interconnect topologies explained

Frequently asked questions about NoC IP cores

What is FlexNoC 5 Interconnect IP?

FlexNoC 5 Interconnect IP is a Network-On-Chip IP core from Arteris listed on Semi IP Hub.

How should engineers evaluate this Network-On-Chip?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Network-On-Chip IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.