MIPI D-PHY IP

The MIPI D-PHY IP (MXL-DPHY) is a high-frequency low-power, low cost, source-synchronous, physical layer compliant with the MIPI®…

Overview

The MIPI D-PHY IP (MXL-DPHY) is a high-frequency low-power, low cost, source-synchronous, physical layer compliant with the MIPI® Alliance Standard for D-PHY. Although primarily used for connecting cameras and display devices to a core processor, this MIPI PHY can also be used for many other applications. It is used in a master-slave configuration, where high-speed signals have a low voltage swing, and low-power signals have large swing. High-speed functions are used for high-speed data traffic while low-power functions are mostly used for control.

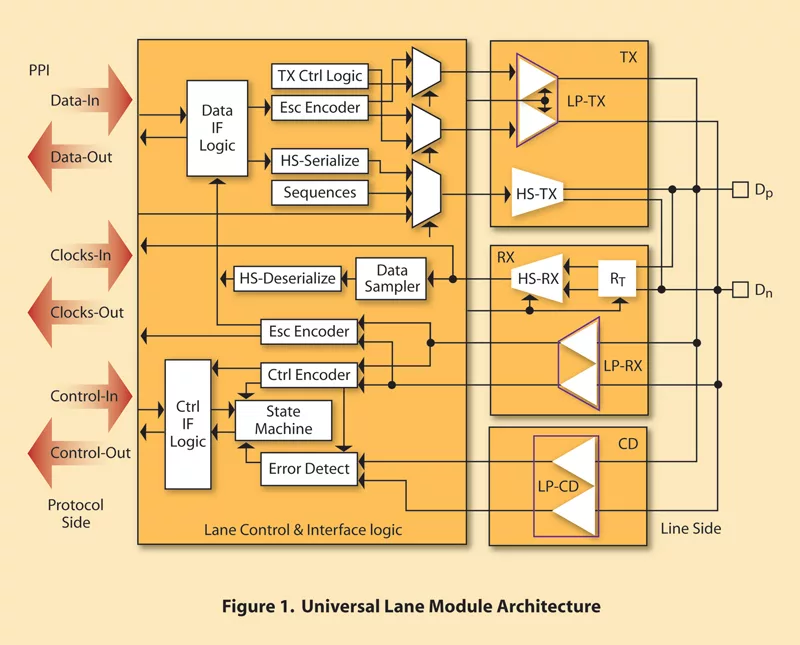

The D-PHY is partitioned into a Digital Module – CIL (Control and Interface Logic) and a Mixed Signal Module. It is provided as a combination of Soft IP views (RTL, and STA Constraints) for Digital Module, and Hard IP views (GDSII/CDL/LEF/LIB) for the Mixed Signal Module. This unique offering of Soft and Hard IP permits architectural design flexibility and seamless implementation in customer-specific design flow.

The CIL module interfaces with the protocol layer and determines the global operation of the lane module. The interface between the D-PHY and the protocol is called the PHY-Protocol Interface (PPI).

During normal operation, the data lane switches between low-power mode and high-speed mode. Bidirectional lanes can also switch communication direction. The change of operating mode or direction requires enabling and disabling certain electrical functions. These enable and disable events do not cause glitches on the lines that would otherwise result in detections of incorrect signal levels. Therefore, all mode and direction changes occur smoothly, ensuring proper detection of the line signals.

The D-PHY is a complete PHY, silicon-proven at multiple foundries and multiple nodes. This MIPI PHY is fully integrated and has analog circuitry, digital, and synthesizable logic. Our D-PHY is built to support the MIPI Camera Serial Interface (CSI) and Display Serial Interface (DSI) using the PHY Protocol Interface (PPI). The vendor has provided this IP in many different configurations to accommodate different applications. The Universal Lane configuration can be used to support any allowed use-case, while other configurations are optimized for many different use cases such as Transmit only, Receive only, DSI, CSI, TX+ and RX+. Both TX+ and RX+ configurations support full-speed loopback operation without the extra area associated with a universal lane configuration.

Key features

- Compliant with MIPI D-PHY Specification v2.5 with backwards compatibility for D-PHY v2.1, v1.2, and v1.1

- The MIPI D-PHY uses point-to-point differential interface and has modular architecture supporting multiple data lanes and a clock lane allowing all possible configurations

- Data lanes support both bidirectional and unidirectional modes, clock lane supports unidirectional communication

- Supports MIPI Camera Serial Interface and MIPI Display Serial Interface (CSI-2, DSI, and DSI-2)

- Supports 80Mbps to 4.5Gbps data rate in high speed mode, 10Mbps data rate in low-power mode

- Universal Lane configuration can be programmed to address any of the allowed use cases

- Configurations optimized for a specific use-case are also available

- Loopback testability (BIST) support

- Optional resistance termination calibrator

- Architected to mate perfectly with our high performance PLLs specifically designed to address MIPI applications up to 4.5Gbps

Block Diagram

Benefits

- Comprehensive embedded DFT features for allowing cost-effective high-volume manufacturing tests

- Support for full-speed internal loopback testability with minimal area overhead for high-volume manufacturing tests in the D-PHY Universal, TX+, and RX+ configurations

- Support for all v2.5 features not available in previous versions of the specifications such as Spread Spectrum Clocking (SSC) and transmit equalization (de-emphasis)

- Support for new power saving functionality such as HS-TX half swing mode and High Speed (HS) unterminated mode

- Support for new Alternate LP Mode, suitable for IoT applications with long channels, enabling Fast Bus Turnaround

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI D-PHY IP?

MIPI D-PHY IP is a MIPI PHY IP core from Mixel, Inc. listed on Semi IP Hub.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.