MIPI CSI2 Interface Solution

Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the…

Overview

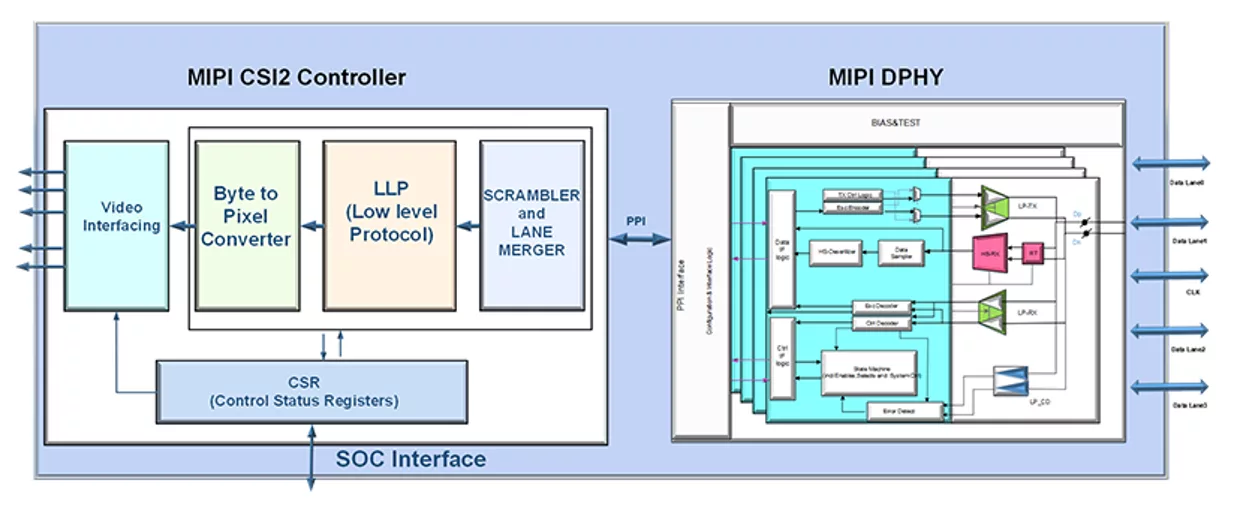

Brite provides full solution for the MIPI CSI interface, which receives the data from sensors in PHY layer, and then converts the byte data to pixel after lane data mergence. Data scramble is an optional feature to decrease the EMI effect. A standard PPI interface is implemented for the connection between MIPI PHY and CSI controller. Brite MIPI CSI interface solution supports image applications with varying pixel formats.

Key features

Controller Features:

- Compliant with MIPI CSI-2 Specification v3.0, v2.1, v2.0, v1.3, v1.1, v1.0

- Compliant with D - PHY Specification v2.1, v2.0, v1.2, v1.1

- Compliant with C - PHY Specification v1.2, v0.7

- Full MIPI CSI-2 RX functionality where either D - PHY / C - PHY can be used

- Supports Multi lane distribution and also lanes can be configured up to 3 lanes for C - PHY and 8 lanes for D - PHY

- Supports Data rate in range 2.5 Gbps

- Supports PPI Interface

- Supports short and long packets

- Supports multilane distribution

- Continuous and non-continuous (gated) D-PHY byte clock support

- Supports Frame and Line Synchronization Packets (Short Packets)

- Supports Data Descrambling in Lanes

- Supports Deskew mechanism for Lane synchronization

- Supports High Speed and Escape Mode (LPDT and ULPS) reception

- Supports the following interleaving methods

- Data type

- Virtual channel

- Supports 16 interleaved Virtual channel in D - PHY and 32 in C - PHY

- Support all Protocol Decoding Level errors

- Supports the compression for RAW data types

- Supports Error Detection techniques for active data using Checksum (16 bit)

- Supports Image applications with varying Pixel formats

- RAW Data Type - RAW6, RAW7, RAW8, RAW10, RAW12, RAW14

- RAW16, RAW20, RAW24

- RGB Data Type - RGB444, RGB555, RGB565, RGB888, RGB 666

- YUV Data Type - YUV422-8bit, YUV422- 10bit, YUV420-8bit

- YUV420- 10bit, Legacy YUV420-8bit

- User defined data type - 8 data types

- Generic 8bit long packet (Null, Blanking, Embedded data)

- Supports Pixel Level /interface with HSYNC, VSYNC, DATA and DATA VALID

- Programmable synchronization and interrupt (error and information) events

- Fully synthesizable

- Static synchronous design

- Positive edge clocking and no internal tri-states

- Scan test ready

- Simple interface allows easy connection to microprocessor/microcontroller devices

PHY Features:

- The Brite MIPI DPHY RX integrates 1 clock lane and up to 4 Data lanes, which is compatible with the D-PHY V1.2 specification.

- The high speed receiver supports 80Mbps up to 2.5Gbps data rate, low-power receiver and transmitter both support data transmission around 10Mbps.

- As the same as TX, the interface is a standard MIPI D-PHY PPI interface that can be easily connected to a standard CSI controller.

Block Diagram

Benefits

- On-die automatic termination calibration to PVT.

- Automatic termination control for HS and LP modes.

- MIPI-HS/MIPI-LP modes Support.

- BIST

- PRBS Checker

Specifications

Identity

Provider

Learn more about MIPI IP core

MIPI MPHY 6.0: Enabling Next-Generation UFS Performance

MIPI: Powering the Future of Connected Devices

Exploring the Latest Innovations in MIPI D-PHY and MIPI C-PHY

New Developments in MIPI's High-Speed Automotive Sensor Connectivity Framework

Streamlining Camera Security Validation Framework Using Synopsys MIPI CSE v2.0 VIP

Frequently asked questions about MIPI IP cores

What is MIPI CSI2 Interface Solution?

MIPI CSI2 Interface Solution is a MIPI IP core from Brite Semiconductor listed on Semi IP Hub.

How should engineers evaluate this MIPI?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.