Highly configurable HW PQC acceleration with RISC-V processor for full CPU offload

configurable HW PQC acceleration with RISC-V processor for full CPU offload, configurable as Subsystem or RoT, with SCA and FIA p…

Overview

Highly configurable HW PQC acceleration with RISC-V processor for full CPU offload, configurable as Subsystem or RoT, with SCA and FIA protection

Engineered for crypto and implementation agility, PQPlatform-TrustSys is optimized for PQ/T hybrid secure boot and features industry-leading protections against power, EM, and fault-injection attacks.

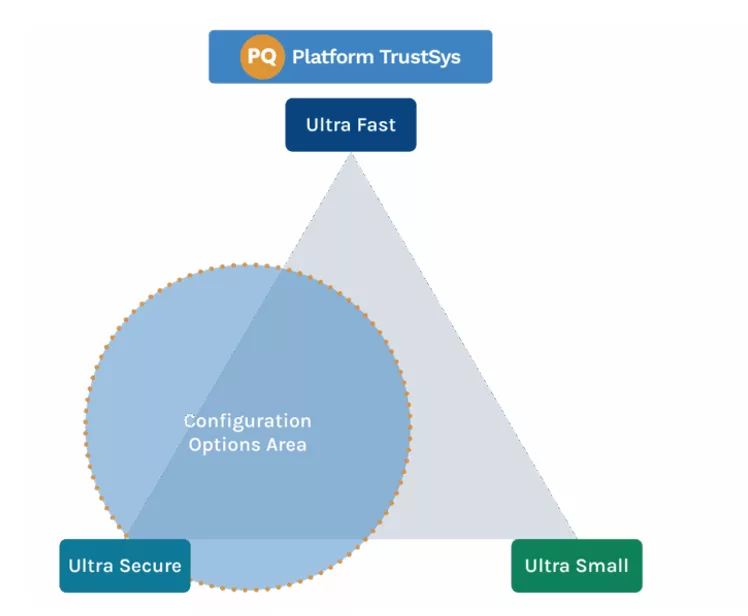

Design Space

PQPlatform-TrustSys scales from a fully autonomous cryptographic hardware subsystem, to a fully-updatable Root of Trust, integrating advanced PQC algorithms alongside traditional standards (ECC, RSA) – fully supporting PQ/T hybrid deployments and legacy compatibility during transition periods. The system includes high-performance accelerators for bulk encryption, hashing, and symmetric cryptography, with seamless support for third-party integration.

Block Diagram

Benefits

- Industry-leading support for PQC algorithms

- Best-in-class secure and efficient

countermeasures against DPA and DFA - Accelerated time-to-market

- Support for CAVP/CMVP and SESIP Compliance

Paths - Support for ECC/RSA, enabling hybrid and legacy

protocols during PQC transition - Advanced accelerators for symmetric cryptography

including AES, SHA-2, SHA-3, HMAC and other bulk

operations - Integration with third-party OTP, PUF and entropy

source components with prevalidated support

from PQShield

Applications

- Device identification and attestation

- Device provisioning

- Secure boot

- Secure firmware update

- Secure product configuration management

- Key storage and management

- Secure debug

- User authentication/authorization

- User data confidentiality and integrity protection

- Cryptographic primitives acceleration

Specifications

Identity

Compute

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Highly configurable HW PQC acceleration with RISC-V processor for full CPU offload?

Highly configurable HW PQC acceleration with RISC-V processor for full CPU offload is a CPU IP core from PQShield listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.