Multi-core capable 64-bit RISC-V CPU with vector extensions

The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the fa…

Overview

The SiFive® Intelligence™ X180 core IP products are designed to meet the increasing requirements of embedded IoT and AI at the far edge. With this 64-bit version, X100 series IP delivers higher performance and better integration with larger memory systems.

The vector engine delivers increased performance for far edge AI and DSP applications, and multiple core interface options provide control and compute assistance for complex coprocessor usages when paired with larger accelerator engines.

Key features

SCALAR PROCESSING

- 64-bit RISC-V ISA

- Dual issue, in-order 8 stage superscalar pipeline

VECTOR PROCESSING

- 128-bit wide vector registers (vlen)

- 64-bit datapath (dlen)

- Int8 and BFloat16 support

- Integer: 2x 32-bit/4x 16-bit/8x 8-bit per cycle

- Floating point: 2x Single precision, 4x Half precision per cycle

- RISC-V Vector Extension v1.0 (RVV1.0)

- In-order sequencing of vector operations (decoupled from scalar execution)

ADDITIONAL SPECS

- Single and multi-core configurations, up to quad-cores

- SiFive Custom Instruction Extension (SCIE)

- Memory port with full duplex load/store bandwidth (8B read + 8B write)

- Up to 16 Physical Memory Protection (PMP) regions

- Optional SiFive WorldGuard security, up to 4 worlds supported

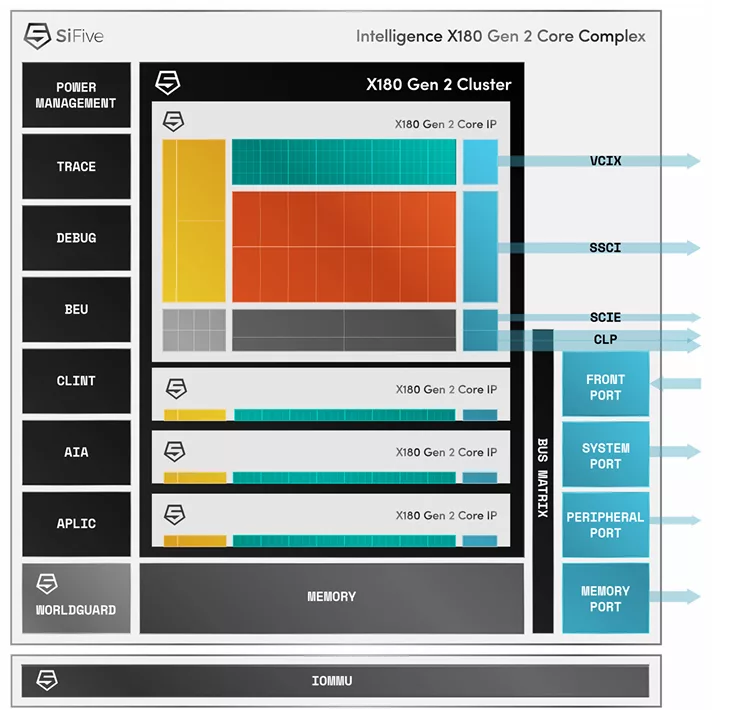

Block Diagram

Benefits

- Efficient Vector Engine provides the ability to accelerate AI models at the far edge using low power and limited silicon area, including filters, transforms, convolutions and AI inference. Also enables acceleration of other functions, such as DSP algorithms.

- Accelerator Control and Assist enables X100 series to be used as an Accelerator Control Unit (ACU), providing accelerator control and assist functions to a customer’s accelerator engine via the specialized co-processor interfaces (SSCI and VCIX). This allows customers to focus on the data processing capabilities and innovations at the platform level and simplifies the software stack.

- Extensive Configurability to match your product requirements and use case.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about CPU IP core

ChiPy®: Bridge Neural Networks and C++ on Silicon — Full Inference Pipelines with Zero CPU Round-Trips

Unleashing Leading On-Device AI Performance and Efficiency with New Arm C1 CPU Cluster

Encarsia: Evaluating CPU Fuzzers via Automatic Bug Injection

Introducing Cortex-A320: Ultra-efficient Armv9 CPU Optimized for IoT

Pie: Pooling CPU Memory for LLM Inference

Frequently asked questions about CPU IP cores

What is Multi-core capable 64-bit RISC-V CPU with vector extensions?

Multi-core capable 64-bit RISC-V CPU with vector extensions is a CPU IP core from Sifive, Inc. listed on Semi IP Hub.

How should engineers evaluate this CPU?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CPU IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.