High Speed Ethernet Quad 10G to 100G PCS

The 100G Ethernet Physical Coding Sublayer (PCS) IP, compliant with the IEEE 802.3 standard, provides a set of features that enab…

Overview

The 100G Ethernet Physical Coding Sublayer (PCS) IP, compliant with the IEEE 802.3 standard, provides a complete set of features that enable users to define an optimized PCS in products across a range of 100G Ethernet applications.

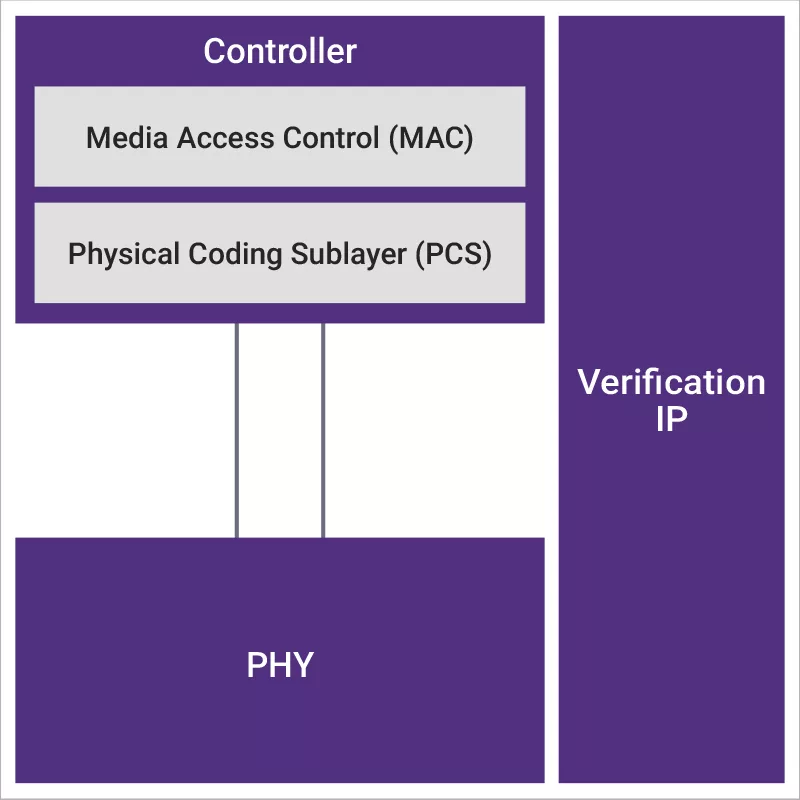

The IP, available in single port or quad port configurations, is designed to be used with the 100G Ethernet MAC IP to deliver a complete system solution. The quad port 100G Ethernet PCS IP can be configured as a 2x100G PCS or a 4x50G/25G/10G PCS interfacing with a 4-lane 56G PHY. The single port IP can be configured as one of 4x25G, 2x50G or 1x100G interfacing with a PHY.

The 100G Ethernet PCS IP offers a comprehensive set of features including 100G scrambler/descrambler, 64b/66b encoder/decoder, multi-lane distribution, alignment marker insertion/striping, block synchronization and gearbox, and clock decoupling FIFOs. The multiplexed Reed-Solomon Forward Error Correction (RS-FEC) function provides different channels at various speeds. The IP implements a CGMII on the application side and four lanes interface to the PHY on the line side.

Key features

- Compliant with the IEEE 802.3 standard

- Configurable IP available in single or quad port for speeds from 1G to 100G

- Designed to be used with Synopsys 100G Ethernet MAC IP for 100G Systems

- Integration tested with the Synopsys 100G Ethernet MAC IP and Synopsys 56G Ethernet PHY IP

- Comprehensive deliverables packaged in an IP-XACT compatible .run file

- Includes Synopsys coreConsultant tool for easy configuration

- Silicon proven

Block Diagram

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is High Speed Ethernet Quad 10G to 100G PCS?

High Speed Ethernet Quad 10G to 100G PCS is a Single-Protocol PHY IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.